# MC9S08LG32 MC9S08LG16

# **Reference Manual**

THIS DOCUMENT CONTAINS INFORMATION ON A NEW PRODUCT UNDER DEVELOPMENT. FREESCALE RESERVES THE RIGHT TO CHANGE OR DISCONTINUE THIS PRODUCT WITHOUT NOTICE.

## HCS08 Microcontrollers

MC9S08LG32RM Rev. 5 8/2009

freescale.com

# MC9S08LG32 Series Features

#### 8-Bit HCS08 Central Processor Unit (CPU)

- Up to 40 MHz CPU at 5.5 V to 2.7 V across temperature range of -40 °C to 85 °C and -40 °C to 105 °C

- HCS08 instruction set with added BGND instruction

- Support for up to 32 interrupt/reset sources

#### **On-Chip Memory**

- 32 KB or 18 KB dual array flash; read/program/erase over full operating voltage and temperature

- 1984 byte random access memory (RAM)

- Security circuitry to prevent unauthorized access to RAM and flash contents

#### **Power-Saving Modes**

- Two low-power stop modes (stop2 and stop3)

- Reduced-power wait mode

- Peripheral clock gating register can disable clocks to unused modules, thereby reducing currents

- Low power on-chip crystal oscillator (XOSC) that can be used in low-power modes to provide accurate clock source to real time counter and LCD controller

- 100 µs typical wakeup time from stop3 mode

#### **Clock Source Options**

- Oscillator (XOSC) Loop-control Pierce oscillator; crystal or ceramic resonator range of 31.25 kHz to 38.4 kHz or 1 MHz to 16 MHz

- Internal Clock Source (ICS) Internal clock source module containing a frequency-locked-loop (FLL) controlled by internal or external reference; precision trimming of internal reference allows 0.2% resolution and 2% deviation over temperature and voltage; supports bus frequencies from 1 MHz to 20 MHz

#### **System Protection**

- COP reset with option to run from dedicated 1 kHz internal clock or bus clock

- Low-voltage warning with interrupt

- Low-voltage detection with reset

- Illegal opcode detection with reset

- · Illegal address detection with reset

- Flash and RAM protection

#### **Development Support**

- Single-wire background debug interface

- Breakpoint capability to allow single breakpoint setting during in-circuit debugging (plus two more breakpoints in on-chip debug module)

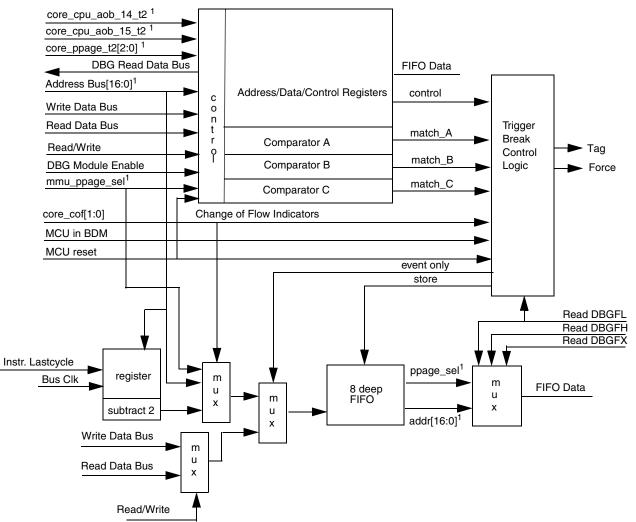

• On-chip in-circuit emulator (ICE) debug module containing three comparators and nine trigger modes; eight deep FIFO for storing change-of-flow addresses and event-only data; debug module supports both tag and force breakpoints

#### Peripherals

- LCD Up to 4 x 41 or 8 x 37 LCD driver with internal charge pump

- ADC Up to 16-channel, 12-bit resolution; 2.5 μs conversion time; automatic compare function; temperature sensor; internal bandgap reference channel; runs in stop3 and can wake up the system; fully functional from 5.5 V to 2.7 V

- SCI Full duplex non-return to zero (NRZ); LIN master extended break generation; LIN slave extended break detection; wakeup on active edge

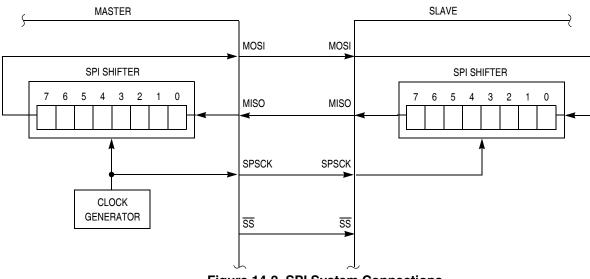

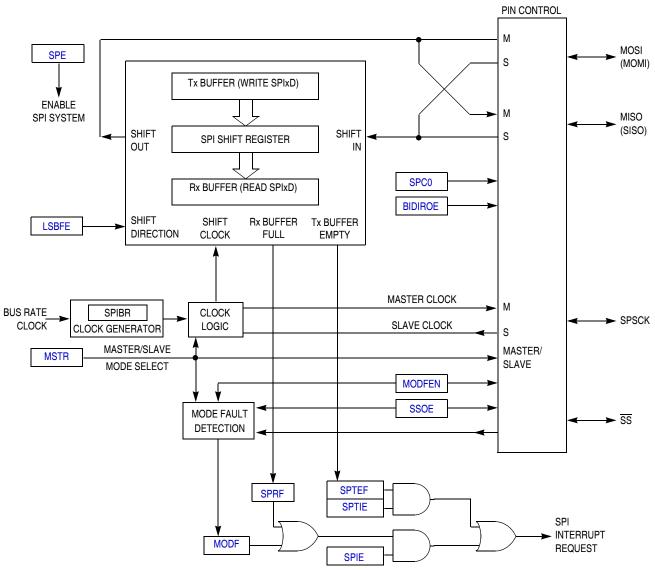

- **SPI** Full-duplex or single-wire bidirectional; double-buffered transmit and receive; master or slave mode; MSB-first or LSB-first shifting

- **IIC** With up to 100 kbps with maximum bus loading; multi-master operation; programmable slave address; interrupt driven byte-by-byte data transfer; supports broadcast mode and 10-bit addressing

- **TPMx** One 6 channel and one 2 channel; selectable input capture, output compare, or buffered edge or center-aligned PWM on each channel

- MTIM 8-bit counter with match register; four clock sources with prescaler dividers; can be used for periodic wakeup

- **RTC** 8-bit modulus counter with binary or decimal based prescaler; three clock sources including one external source; can be used for time base, calendar, or task scheduling functions

- **KBI** One keyboard control module capable of supporting 8x8 keyboard matrix

- IRQ External pin for wakeup from low-power modes

#### Input/Output

- 39, 53, or 69 GPIOs

- 8 KBI and 1 IRQ interrupt with selectable polarity

- Hysteresis and configurable pullup device on all input pins; configurable slew rate and drive strength on all output pins

#### **Package Options**

• 48-pin LQFP, 64-pin LQFP, and 80-pin LQFP

# MC9S08LG32 Reference Manual

# Covers MC9S08LG32 MC9S08LG16

THIS DOCUMENT CONTAINS INFORMATION ON A NEW PRODUCT UNDER DEVELOPMENT. FREESCALE RESERVES THE RIGHT TO CHANGE OR DISCONTINUE THIS PRODUCT WITHOUT NOTICE.

#### **Related Documentation:**

- MC9S08LG32PB (Product Brief) Contains descriptive feature set, example application information, and developer environment details

- MC9S08LG32 Data Sheet Contains package information, pinouts, electricals/characterization data, and mechanical drawings

Find the most current versions of all documents at: http://www.freescale.com MC9S08LG32RM Rev. 5 8/2009

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. © Freescale Semiconductor, Inc., 2009. All rights reserved.

### **Revision History**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://www.freescale.com

The following revision history table summarizes changes contained in this document.

| Revision<br>Number | Revision<br>Date | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 1             | 9/2008           | First Initial Release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Rev. 2             | 9/2008           | Second Initial Release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Rev. 3             | 11/2008          | Alpha Customer Release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Rev. 4             | 2/2009           | Launch Release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Rev. 5             | 8/2009           | <ul> <li>In Chapter 3, "Modes of Operation," added On-Chip Peripheral Modules in<br/>Stop Modes section in Chapter 3.</li> <li>In Table 5-2, corrected addresses for vector number from 23 to 18.</li> <li>In Table 7-1, updated KBI pins order as per PINPS1 register.</li> <li>Changed TCLK, T1CH0, T1CH1, T2CH0, T2CH1, T2CH2, T2CH3, T2CH4,<br/>T2CH5 to TPMCLK, TPM1CH0, TPM1CH1, TPM2CH0, TPM2CH1,<br/>TPM2CH2, TPM2CH3, TPM2CH4, TPM2CH5.</li> <li>Changed 'LCDCPEN" to "LCDPEN" and "LCDFWF" to "LCDWF."</li> <li>In Chapter 12, "Inter-Integrated Circuit (S08IICV2)," a note is added in the<br/>introduction mentioning that MC9S08LG32 series of MCUs include only one<br/>IIC module.</li> </ul> |

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. © Freescale Semiconductor, Inc., 2009. All rights reserved.

# List of Chapters

| je |

|----|

|    |

| Chapter 1 Device Overview                                |

|----------------------------------------------------------|

| Chapter 2 Pins and Connections                           |

| Chapter 3 Modes of Operation                             |

| Chapter 4 Memory                                         |

| Chapter 5 Resets, Interrupts, and General System Control |

| Chapter 6 Parallel Input/Output Control                  |

| Chapter 7 Keyboard Interrupt (S08KBIV2)                  |

| Chapter 8 Central Processor Unit (S08CPUV5)              |

| Chapter 9 LCD Module (S08LCDLPV1)                        |

| Chapter 10 Analog-to-Digital Converter (S08ADC12V1)      |

| Chapter 11 Internal Clock Source (S08ICSV3)              |

| Chapter 12 Inter-Integrated Circuit (S08IICV2)           |

| Chapter 13 Serial Communications Interface (S08SCIV4)    |

| Chapter 14 Serial Peripheral Interface (S08SPIV4)278     |

| Chapter 15 Real-Time Counter (S08RTCV1)                  |

| Chapter 16 Timer/Pulse-Width Modulator (S08TPMV3)        |

| Chapter 17 Modulo Timer (S08MTIMV1)                      |

| Chapter 18 Development Support                           |

| Chapter 19 Debug Module (DBG) (64K)                      |

# Contents

**Section Number**

Page

### Chapter 1 Device Overview

| 1.1 | Devices in the MC9S08LG32 Series | 21 |

|-----|----------------------------------|----|

| 1.2 | MCU Block Diagram                | 22 |

|     | System Clock Distribution        |    |

### Chapter 2 Pins and Connections

| Introdu | ction                                                                  | 27                                                                                                                                                                                                                                                                                                                                                   |

|---------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device  | Pin Assignment                                                         | 27                                                                                                                                                                                                                                                                                                                                                   |

|         |                                                                        |                                                                                                                                                                                                                                                                                                                                                      |

|         |                                                                        |                                                                                                                                                                                                                                                                                                                                                      |

| 2.3.2   | Oscillator                                                             |                                                                                                                                                                                                                                                                                                                                                      |

| 2.3.3   | RESET                                                                  |                                                                                                                                                                                                                                                                                                                                                      |

| 2.3.4   | Background / Mode Select (BKGD/MS)                                     |                                                                                                                                                                                                                                                                                                                                                      |

|         | • • • • • • • • • • • • • • • • • • •                                  |                                                                                                                                                                                                                                                                                                                                                      |

| 2.3.6   | LCD Pins                                                               |                                                                                                                                                                                                                                                                                                                                                      |

| 2.3.7   | General-Purpose I/O (GPIO) and Peripheral Ports                        |                                                                                                                                                                                                                                                                                                                                                      |

|         | Device<br>Recomm<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4<br>2.3.5<br>2.3.6 | Introduction         Device Pin Assignment         Recommended System Connections         2.3.1       Power         2.3.2       Oscillator         2.3.3       RESET         2.3.4       Background / Mode Select (BKGD/MS)         2.3.5       IRQ         2.3.6       LCD Pins         2.3.7       General-Purpose I/O (GPIO) and Peripheral Ports |

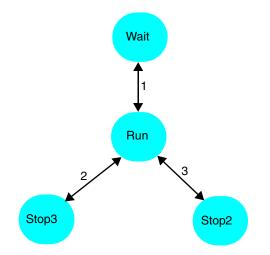

### Chapter 3 Modes of Operation

| 3.1 | Introdu      | ction                                    | 41 |

|-----|--------------|------------------------------------------|----|

| 3.2 | Feature      | S                                        | 41 |

| 3.3 | Run Mo       | ode                                      | 41 |

|     |              | Background Mode                          |    |

| 3.5 |              | ode                                      |    |

| 3.6 | 5 Stop Modes |                                          | 43 |

|     |              | Stop2 Mode                               |    |

|     | 3.6.2        | Stop3 Mode                               | 44 |

|     | 3.6.3        | Active BDM Enabled in Stop Mode          | 45 |

|     | 3.6.4        | LVD Enabled in Stop Mode                 | 45 |

| 3.7 | Mode S       | Selection                                | 45 |

|     | 3.7.1        | On-Chip Peripheral Modules in Stop Modes | 48 |

|     |              |                                          |    |

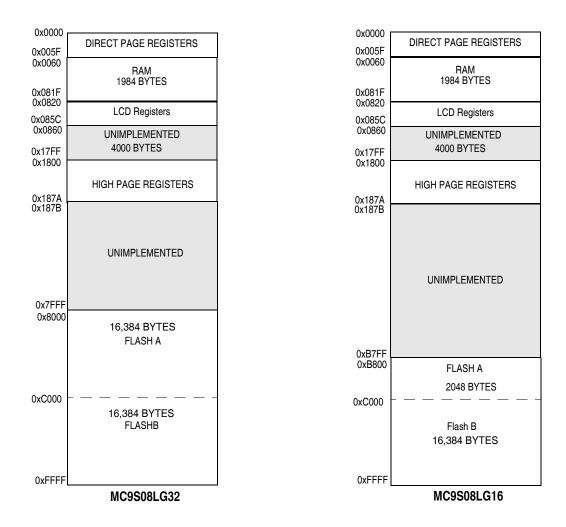

#### Chapter 4 Memory

### Title

### Page

| 4.2 | MC9S0                            | 8LG32 Series Memory Map                      |    |

|-----|----------------------------------|----------------------------------------------|----|

| 4.3 | Reset an                         | nd Interrupt Vector Assignments              |    |

| 4.4 | Registe                          | r Addresses and Bit Assignments              |    |

|     | -                                | Reserved Flash Locations                     |    |

| 4.5 | RAM                              |                                              | 60 |

| 4.6 | Flash                            |                                              | 60 |

|     | 4.6.1                            | Features                                     | 61 |

|     | 4.6.2                            | Program and Erase Times                      | 61 |

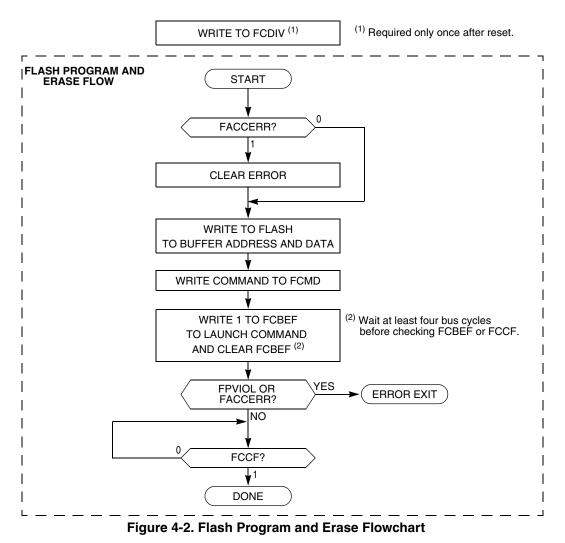

|     | 4.6.3                            | Program and Erase Command Execution          | 62 |

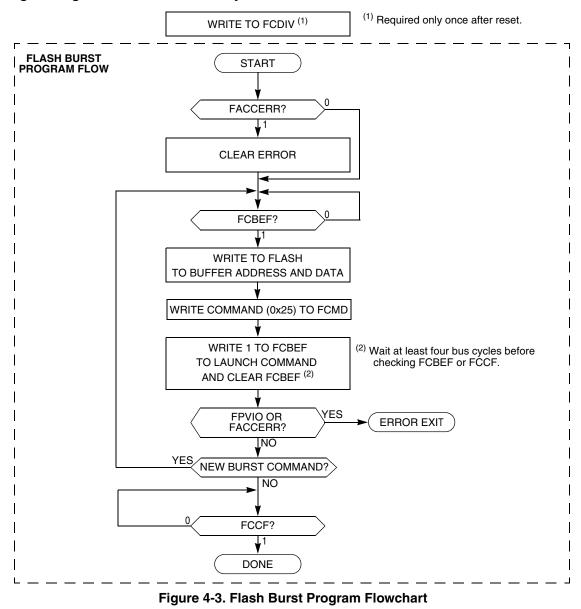

|     | 4.6.4                            | Burst Program Execution                      | 63 |

|     | 4.6.5                            | Access Errors                                | 65 |

|     | 4.6.6                            | Flash Block Protection                       | 65 |

|     | 4.6.7                            | Vector Redirection                           | 66 |

| 4.7 | Security                         | У                                            | 66 |

| 4.8 | Flash Registers and Control Bits |                                              | 67 |

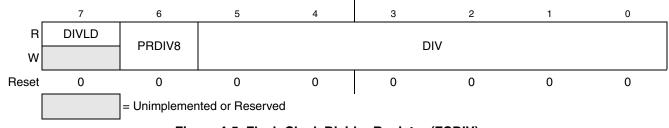

|     | 4.8.1                            | Flash Clock Divider Register (FCDIV)         | 68 |

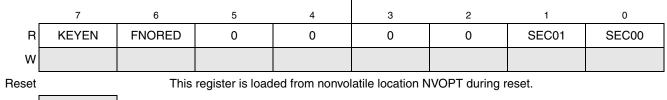

|     | 4.8.2                            | Flash Options Register (FOPT and NVOPT)      | 69 |

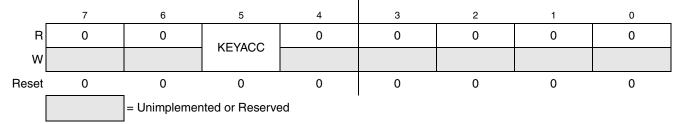

|     | 4.8.3                            | Flash Configuration Register (FCNFG)         | 70 |

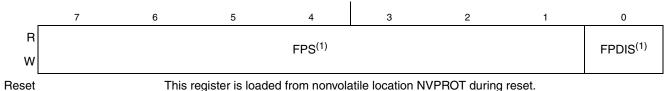

|     | 4.8.4                            | Flash Protection Register (FPROT and NVPROT) |    |

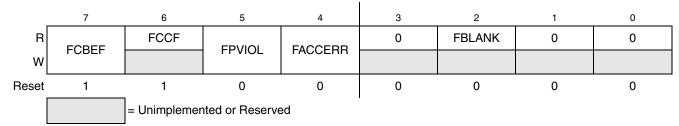

|     | 4.8.5                            | Flash Status Register (FSTAT)                |    |

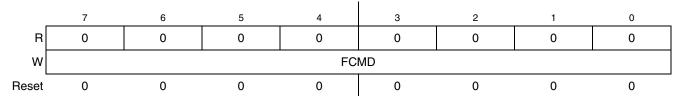

|     | 4.8.6                            | Flash Command Register (FCMD)                |    |

# Chapter 5 Resets, Interrupts, and General System Control

| 5.1 | Introduction                                                    | 73 |

|-----|-----------------------------------------------------------------|----|

| 5.2 | Features                                                        |    |

| 5.3 | MCU Reset                                                       | 73 |

| 5.4 | Computer Operating Properly (COP) Watchdog                      | 74 |

| 5.5 | Interrupts                                                      | 75 |

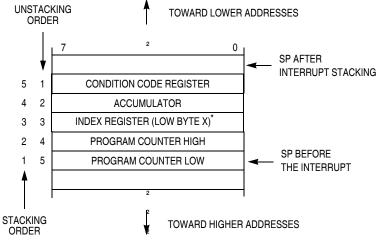

|     | 5.5.1 Interrupt Stack Frame                                     | 76 |

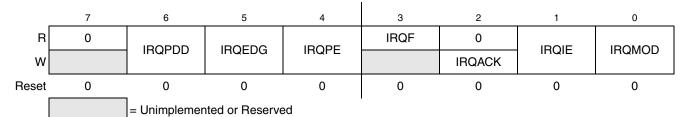

|     | 5.5.2 External Interrupt Request (IRQ) Pin                      | 76 |

|     | 5.5.3 Interrupt Vectors, Sources, and Local Masks               | 77 |

| 5.6 | Low-Voltage Detect (LVD) System                                 |    |

|     | 5.6.1 Power-On Reset Operation                                  | 79 |

|     | 5.6.2 Low-Voltage Detection (LVD) Reset Operation               | 79 |

|     | 5.6.3 Low-Voltage Warning (LVW) Interrupt Operation             | 79 |

| 5.7 | Peripheral Clock Gating                                         | 79 |

| 5.8 | Reset, Interrupt, and System Control Registers and Control Bits | 80 |

|     | 5.8.1 Interrupt Pin Request Status and Control Register (IRQSC) | 80 |

|     | 5.8.2 System Reset Status Register (SRS)                        |    |

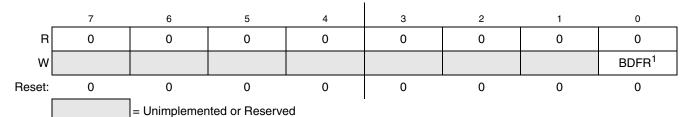

|     | 5.8.3 System Background Debug Force Reset Register (SBDFR)      |    |

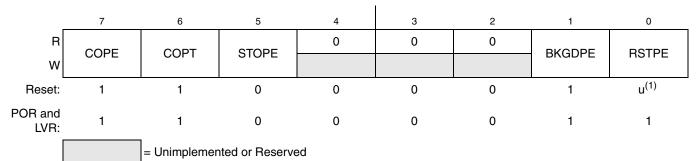

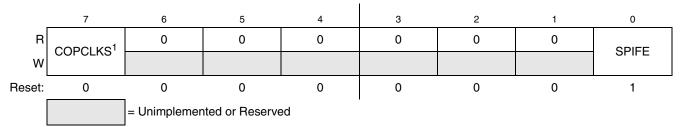

|     | 5.8.4 System Options Register 1 (SOPT1)                         | 84 |

|     |                                                                 |    |

### Title

### Page

| 5.8.5  | System Options Register 2 (SOPT2)                              |    |

|--------|----------------------------------------------------------------|----|

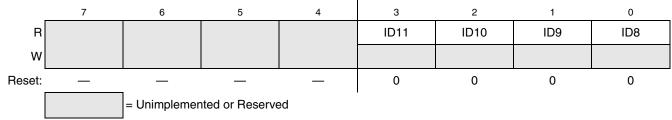

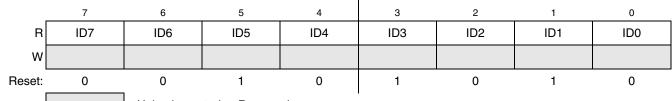

|        | System Device Identification Register (SDIDH, SDIDL)           |    |

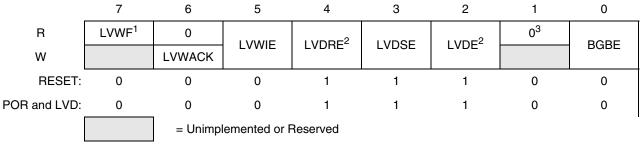

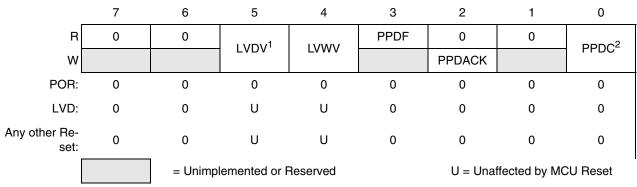

| 5.8.7  | System Power Management Status and Control 1 Register (SPMSC1) |    |

| 5.8.8  | System Power Management Status and Control 2 Register (SPMSC2) |    |

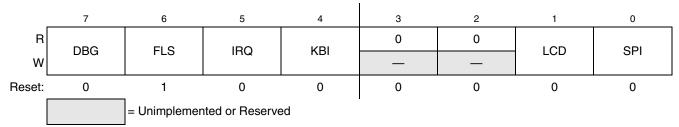

| 5.8.9  | System Clock Gating Control 1Register (SCGC1)                  | 90 |

| 5.8.10 | System Clock Gating Control 2 Register (SCGC2)                 | 91 |

| 5.8.11 | Pin Position Control Register (PINPS1)                         |    |

| 5.8.12 | Pin Position Control Register (PINPS2)                         |    |

| 5.8.13 | Pin Position Control Register (PINPS3)                         | 94 |

| 5.8.14 | Pin Position Control Register (PINPS4)                         |    |

# Chapter 6 Parallel Input/Output Control

| 6.1 | Introdu  | ction                         | 97  |

|-----|----------|-------------------------------|-----|

| 6.2 | Pins Sh  | ared with LCD                 | 97  |

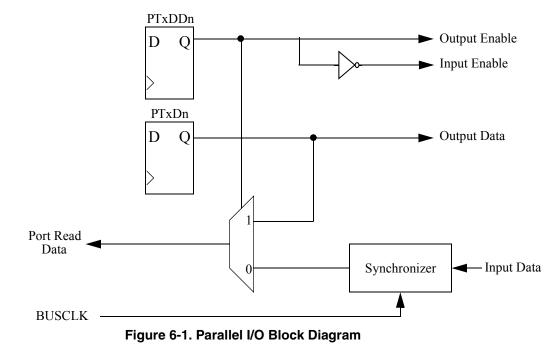

| 6.3 | Port Da  | ta and Data Direction         | 97  |

| 6.4 | Pullup,  | Slew Rate, and Drive Strength | 98  |

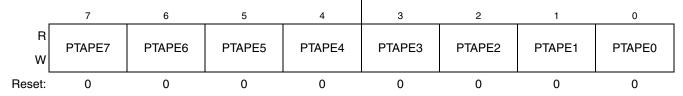

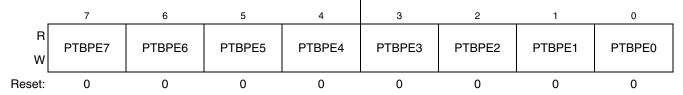

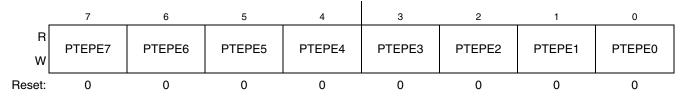

|     | 6.4.1    | Port Internal Pullup Enable   | 98  |

|     | 6.4.2    | Port Slew Rate Enable         | 99  |

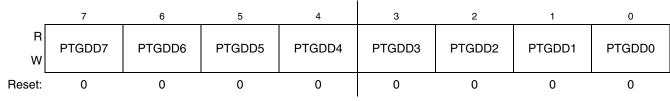

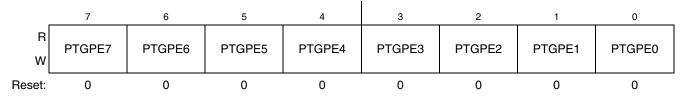

|     | 6.4.3    | Port Drive Strength Select    | 99  |

| 6.5 | Open D   | rain Operation                | 99  |

| 6.6 | Pin Beh  | avior in Stop Modes           | 99  |

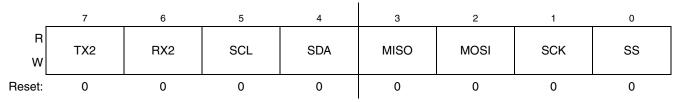

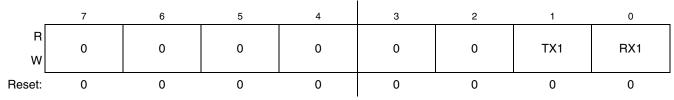

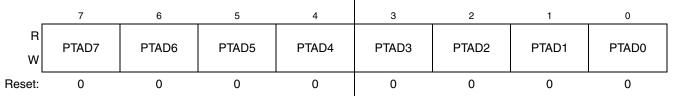

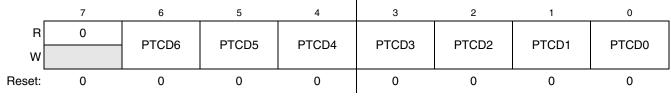

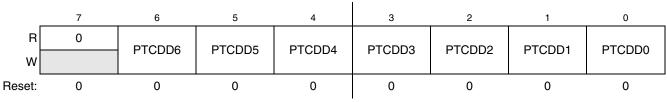

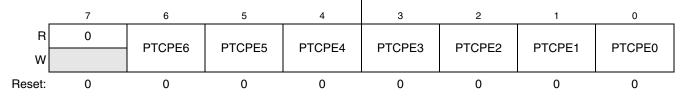

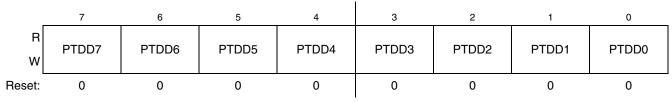

| 6.7 | Parallel | I/O and Pin Control Registers | 100 |

|     | 6.7.1    | Port A Registers              | 100 |

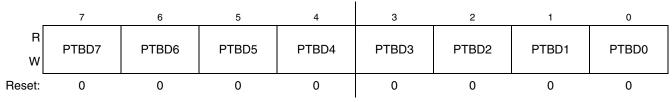

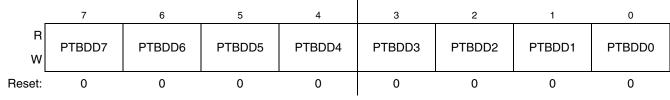

|     | 6.7.2    | Port B Registers              | 104 |

|     | 6.7.3    | Port C Registers              | 107 |

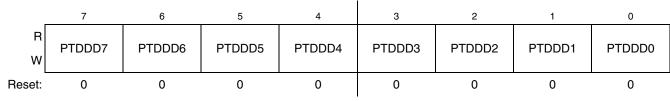

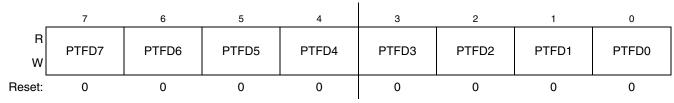

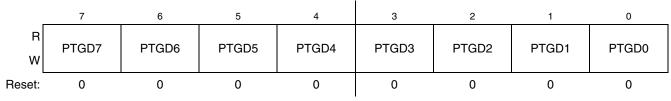

|     | 6.7.4    | Port D Registers              | 110 |

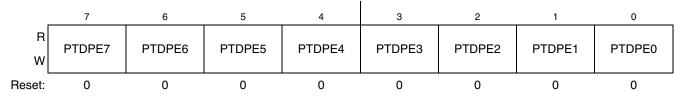

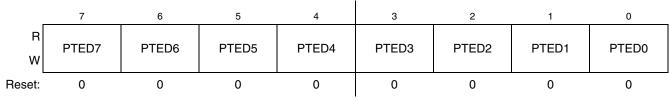

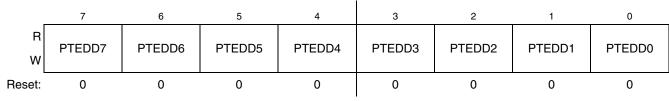

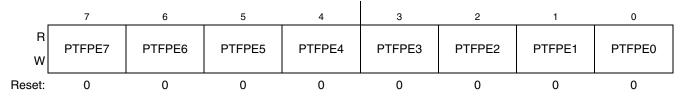

|     | 6.7.5    | Port E Registers              | 113 |

|     | 6.7.6    | Port F Registers              | 116 |

|     | 6.7.7    | Port G Registers              | 119 |

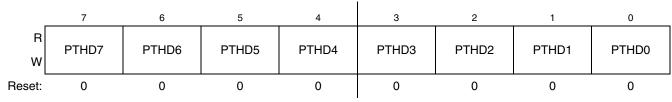

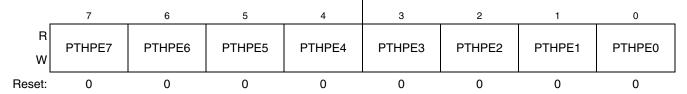

|     | 6.7.8    | Port H Registers              | 122 |

|     | 6.7.9    | Port I Registers              | 125 |

|     |          |                               |     |

### Chapter 7 Keyboard Interrupt (S08KBIV2)

| 7.1 | Introduc | ction                |  |

|-----|----------|----------------------|--|

|     | 7.1.1    | Module Configuration |  |

|     |          | KBI Clock Gating     |  |

|     |          | Features             |  |

|     | 7.1.4    | Modes of Operation   |  |

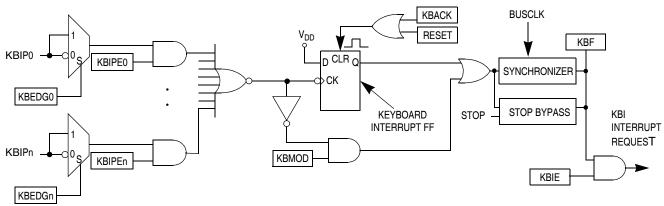

|     | 7.1.5    | Block Diagram        |  |

| 7.2 |          | l Signal Description |  |

Title

### Page

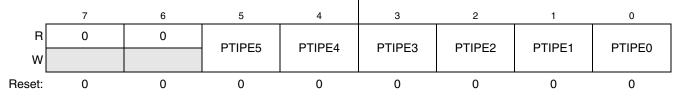

| 7.3 | Registe | r Definition                            | 131 |

|-----|---------|-----------------------------------------|-----|

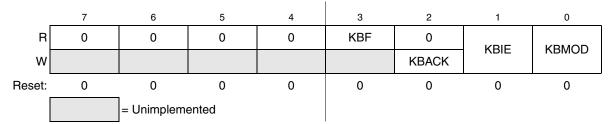

|     |         | KBI Status and Control Register (KBISC) |     |

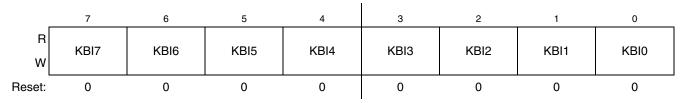

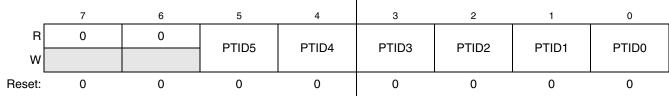

|     | 7.3.2   | KBI Pin Enable Register (KBIPE)         | 132 |

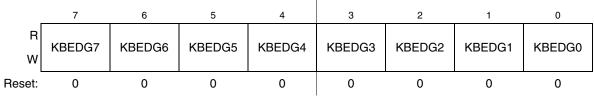

|     |         | KBI Edge Select Register (KBIES)        |     |

|     |         | nal Description                         | 133 |

|     |         | Edge Only Sensitivity                   |     |

|     | 7.4.2   | Edge and Level Sensitivity              | 133 |

|     | 7.4.3   | KBI Pullup/Pulldown Resistors           | 134 |

|     | 7.4.4   | KBI Initialization                      | 134 |

### Chapter 8 Central Processor Unit (S08CPUV5)

| 8.1 | Introdu | ction                           | 135 |

|-----|---------|---------------------------------|-----|

|     | 8.1.1   | Features                        | 135 |

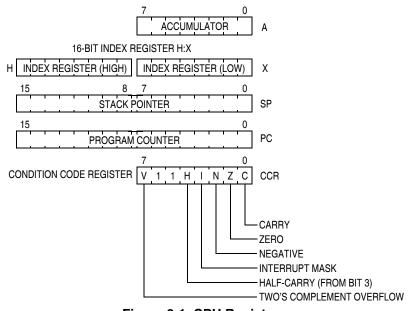

| 8.2 | Program | nmer's Model and CPU Registers  | 136 |

|     | 8.2.1   | Accumulator (A)                 | 136 |

|     | 8.2.2   | Index Register (H:X)            | 136 |

|     | 8.2.3   | Stack Pointer (SP)              | 137 |

|     | 8.2.4   | Program Counter (PC)            | 137 |

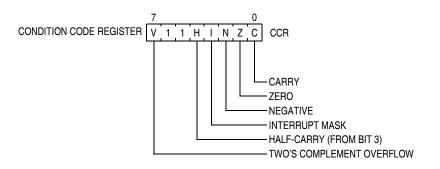

|     | 8.2.5   | Condition Code Register (CCR)   | 137 |

| 8.3 | Address | sing Modes                      |     |

|     | 8.3.1   | Inherent Addressing Mode (INH)  | 139 |

|     | 8.3.2   | Relative Addressing Mode (REL)  | 139 |

|     | 8.3.3   | Immediate Addressing Mode (IMM) | 139 |

|     | 8.3.4   | Direct Addressing Mode (DIR)    | 139 |

|     | 8.3.5   | Extended Addressing Mode (EXT)  | 140 |

|     | 8.3.6   | Indexed Addressing Mode         | 140 |

| 8.4 | Special | Operations                      | 141 |

|     | 8.4.1   | Reset Sequence                  | 141 |

|     | 8.4.2   | Interrupt Sequence              | 141 |

|     | 8.4.3   | Wait Mode Operation             | 142 |

|     | 8.4.4   | Stop Mode Operation             | 142 |

|     | 8.4.5   | BGND Instruction                | 143 |

| 8.5 | HCS08   | Instruction Set Summary         |     |

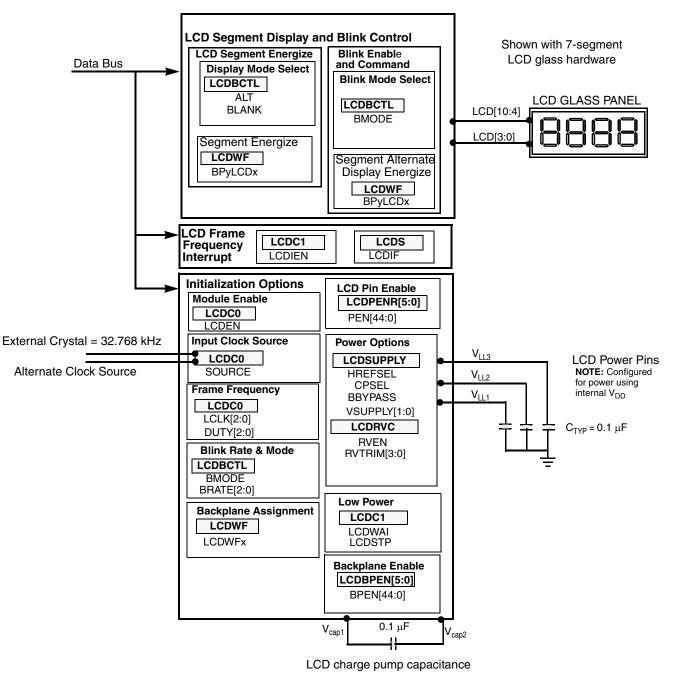

## Chapter 9 LCD Module (S08LCDLPV1)

| 9.1 | Introdu | ction                         |  |

|-----|---------|-------------------------------|--|

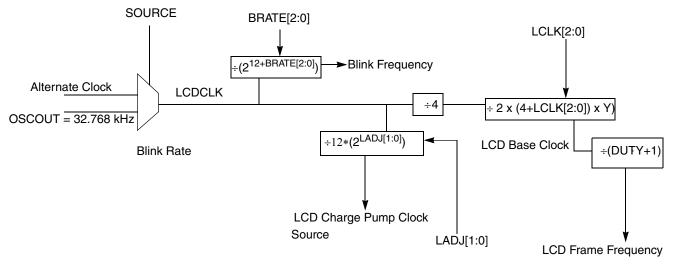

|     |         | LCD Clock Sources             |  |

|     |         | LCD Modes of Operation        |  |

|     |         | LCD Status after Stop2 Wakeup |  |

|     |         | LCD Clock Gating              |  |

|     |         | 5                             |  |

|     | 9.1.5   | Features                                                     | 160 |

|-----|---------|--------------------------------------------------------------|-----|

|     | 9.1.6   | Modes of Operation                                           | 161 |

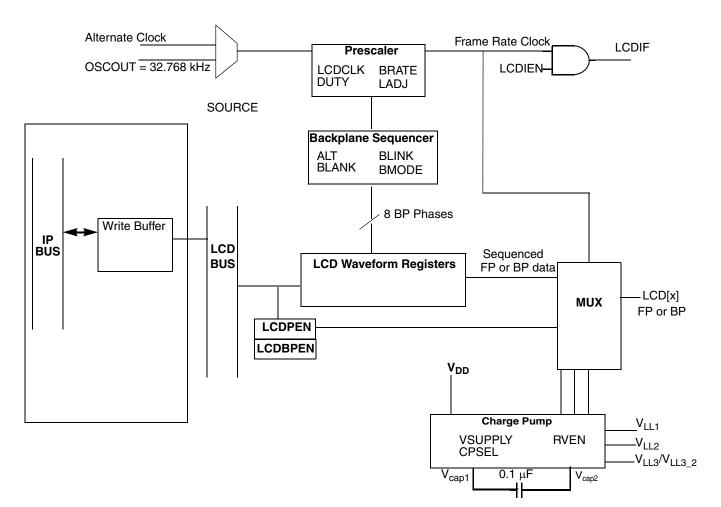

|     | 9.1.7   | Block Diagram                                                | 161 |

| 9.2 | Externa | 1 Signal Description                                         |     |

|     | 9.2.1   | LCD[44:0]                                                    |     |

|     | 9.2.2   | $V_{LL1}, V_{LL2}, V_{LL3}$                                  |     |

|     | 9.2.3   | $V_{cap1}, V_{cap2}$                                         |     |

| 9.3 | Registe | r Definition                                                 | 163 |

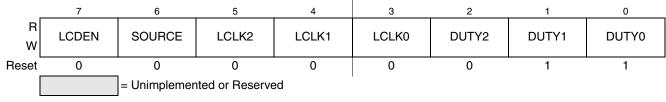

|     | 9.3.1   | LCD Control Register 0 (LCDC0)                               | 163 |

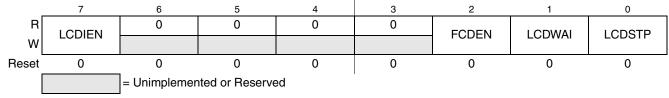

|     | 9.3.2   | LCD Control Register 1 (LCDC1)                               |     |

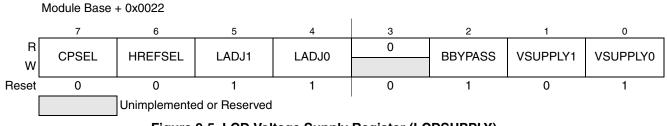

|     | 9.3.3   | LCD Voltage Supply Register (LCDSUPPLY)                      | 165 |

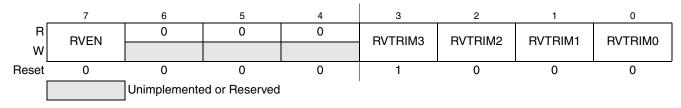

|     | 9.3.4   | LCD Regulated Voltage Control Register (LCDRVC)              | 166 |

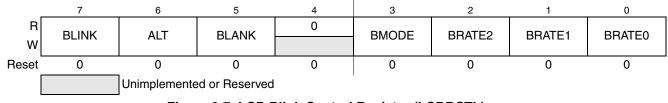

|     | 9.3.5   | LCD Blink Control Register (LCDBCTL)                         | 167 |

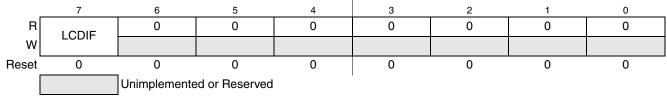

|     | 9.3.6   | LCD Status Register (LCDS)                                   |     |

|     | 9.3.7   | LCD Pin Enable Registers 0–5 (LCDPEN0–LCDPEN5)               |     |

|     | 9.3.8   | Backplane Enable Registers 0–5 (BPEN0–BPEN5)                 |     |

|     | 9.3.9   | LCD Waveform Registers (LCDWF[44:0])                         | 170 |

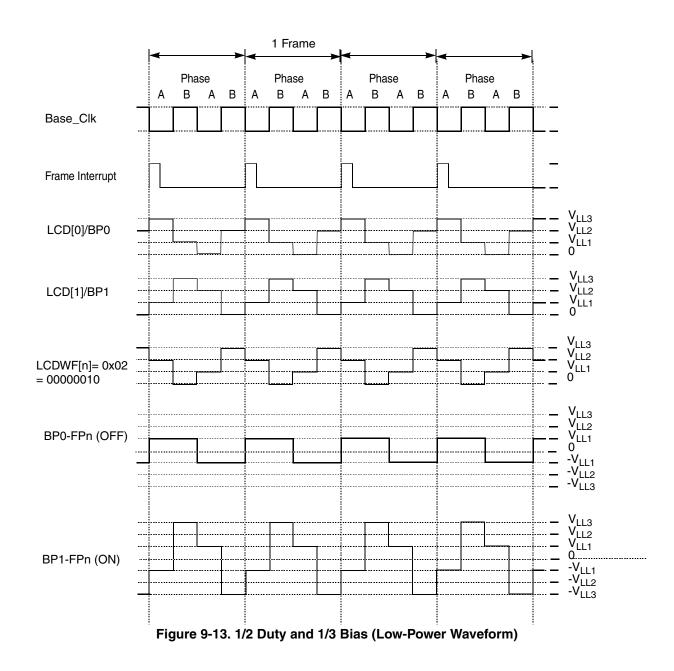

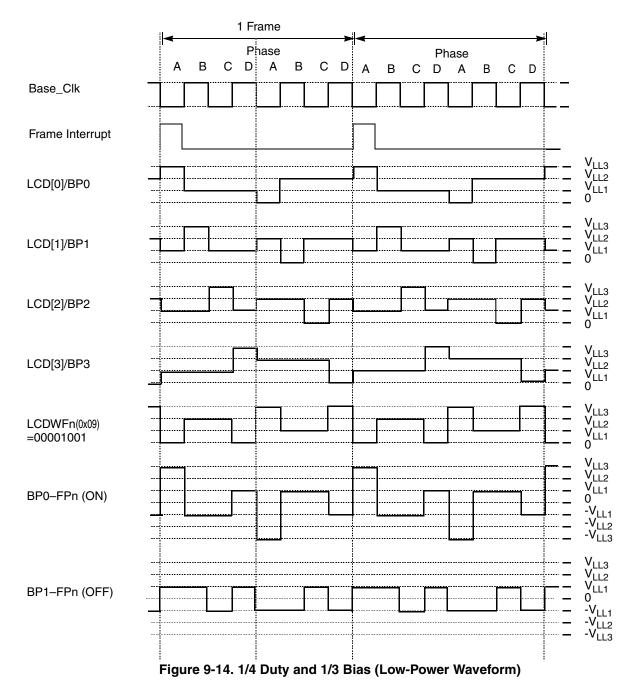

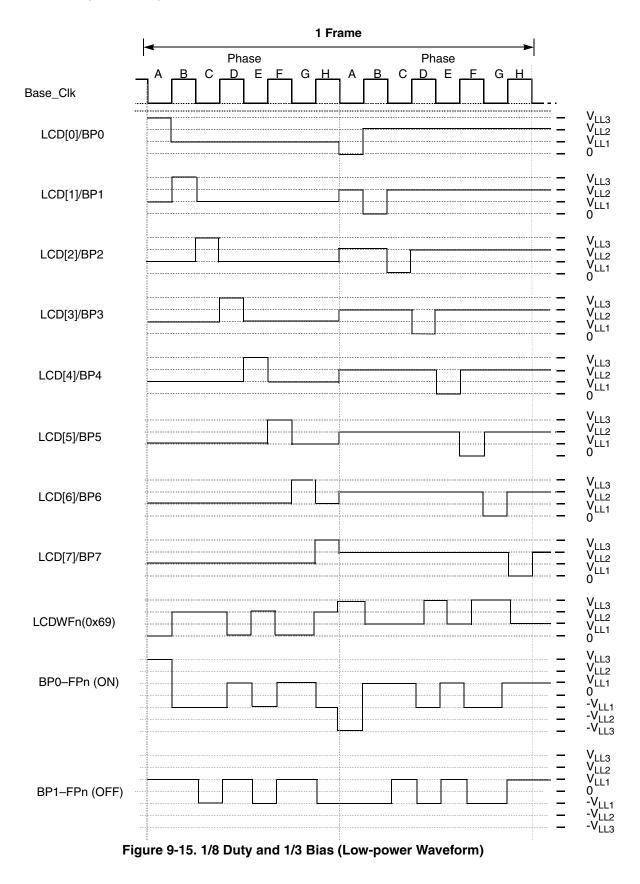

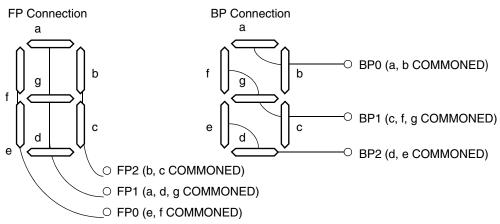

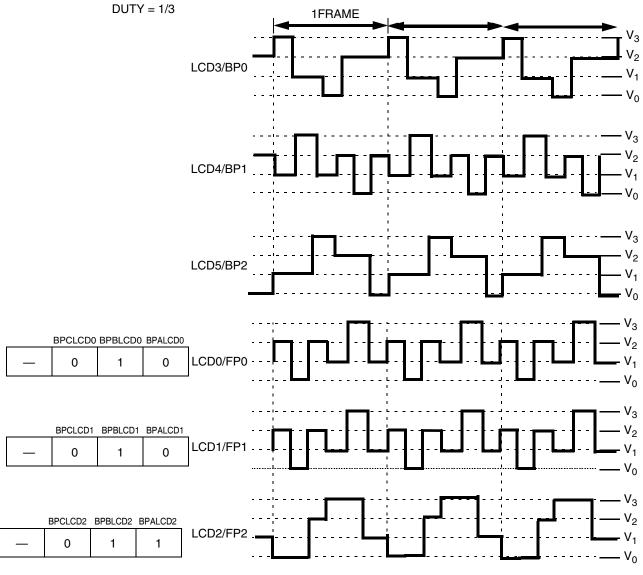

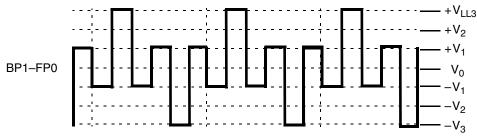

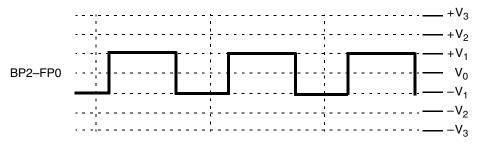

| 9.4 | Functio | nal Description                                              | 174 |

|     | 9.4.1   | LCD Driver Description                                       |     |

|     | 9.4.2   | LCDWF Registers                                              |     |

|     | 9.4.3   | LCD Display Modes                                            |     |

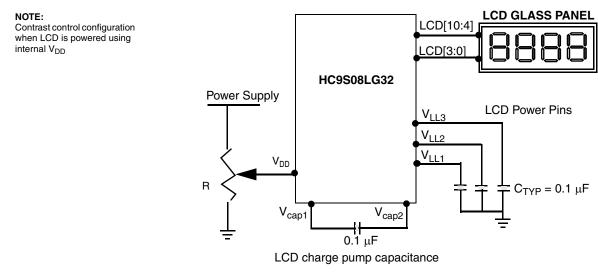

|     | 9.4.4   | LCD Charge Pump, Voltage Divider, and Power Supply Operation |     |

|     | 9.4.5   | Resets                                                       |     |

|     | 9.4.6   | Interrupts                                                   |     |

| 9.5 |         | ation Section                                                |     |

|     | 9.5.1   | Initialization Sequence                                      |     |

|     | 9.5.2   | Initialization Examples                                      |     |

| 9.6 | 11      | tion Information                                             |     |

|     | 9.6.1   | LCD Seven Segment Example Description                        |     |

|     | 9.6.2   | LCD Contrast Control                                         |     |

|     | 9.6.3   | Stop Mode Recovery                                           | 199 |

Title

## Chapter 10 Analog-to-Digital Converter (S08ADC12V1)

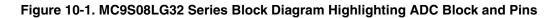

| 10.1 | Introduction                            |  |

|------|-----------------------------------------|--|

|      | 10.1.1 ADC shared with LCD              |  |

|      | 10.1.2 ADC Reference and Supply Voltage |  |

|      | 10.1.3 ADC Clock Gating                 |  |

|      | 10.1.4 Module Configurations            |  |

|      | 10.1.5 Features                         |  |

|      | 10.1.6 ADC Module Block Diagram         |  |

| 10.2 | External Signal Description             |  |

MC9S08LG32 MCU Series, Rev. 5

**Section Number**

# Page

### Title

### Page

|      | 10.2.1 Analog Power (V <sub>DDA</sub> )            |     |

|------|----------------------------------------------------|-----|

|      | 10.2.2 Analog Ground ( $V_{SSA}$ )                 | 206 |

|      | 10.2.3 Voltage Reference High (V <sub>REFH</sub> ) | 206 |

|      | 10.2.4 Voltage Reference Low (V <sub>REFL</sub> )  |     |

|      | 10.2.5 Analog Channel Inputs (ADx)                 |     |

| 10.3 | Register Definition                                |     |

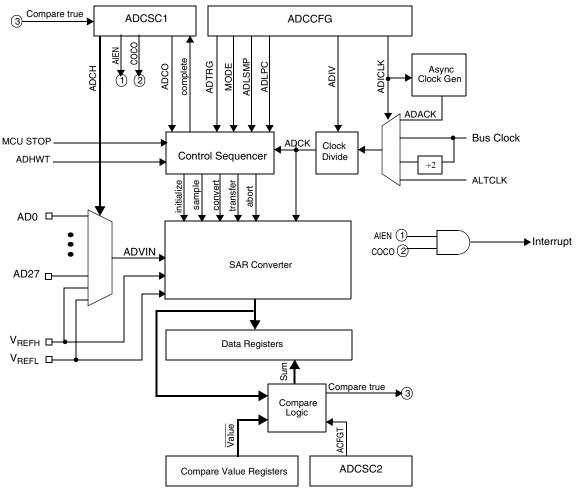

|      | 10.3.1 Status and Control Register 1 (ADCSC1)      | 206 |

|      | 10.3.2 Status and Control Register 2 (ADCSC2)      | 208 |

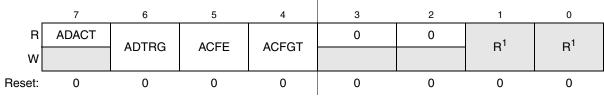

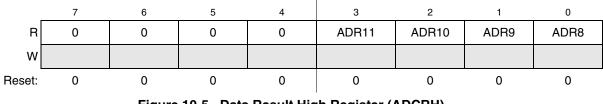

|      | 10.3.3 Data Result High Register (ADCRH)           |     |

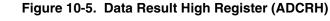

|      | 10.3.4 Data Result Low Register (ADCRL)            |     |

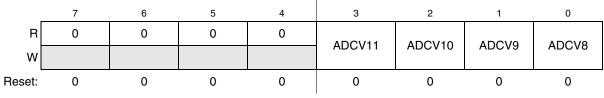

|      | 10.3.5 Compare Value High Register (ADCCVH)        | 209 |

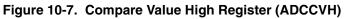

|      | 10.3.6 Compare Value Low Register (ADCCVL)         | 210 |

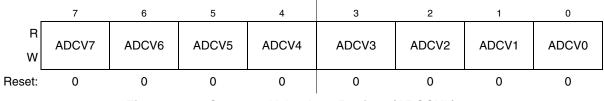

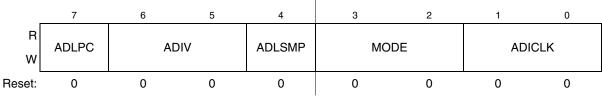

|      | 10.3.7 Configuration Register (ADCCFG)             | 210 |

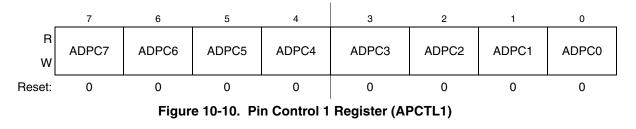

|      | 10.3.8 Pin Control 1 Register (APCTL1)             | 211 |

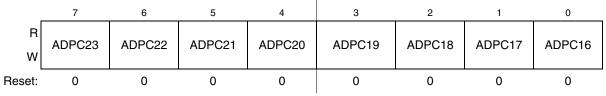

|      | 10.3.9 Pin Control 2 Register (APCTL2)             | 212 |

|      | 10.3.10Pin Control 3 Register (APCTL3)             | 213 |

| 10.4 | Functional Description                             | 214 |

|      | 10.4.1 Clock Select and Divide Control             |     |

|      | 10.4.2 Input Select and Pin Control                | 215 |

|      | 10.4.3 Hardware Trigger                            |     |

|      | 10.4.4 Conversion Control                          | 215 |

|      | 10.4.5 Automatic Compare Function                  | 218 |

|      | 10.4.6 MCU Wait Mode Operation                     | 218 |

|      | 10.4.7 MCU Stop3 Mode Operation                    | 219 |

|      | 10.4.8 MCU Stop2 Mode Operation                    | 219 |

| 10.5 |                                                    |     |

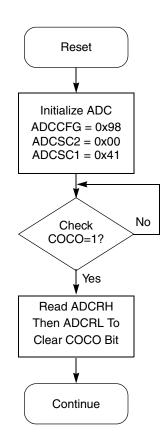

|      | 10.5.1 ADC Module Initialization Example           | 220 |

| 10.6 | Application Information                            |     |

|      | 10.6.1 External Pins and Routing                   |     |

|      | 10.6.2 Sources of Error                            |     |

# Chapter 11 Internal Clock Source (S08ICSV3)

| 11.1 | Introduction                          |  |

|------|---------------------------------------|--|

|      | 11.1.1 Features                       |  |

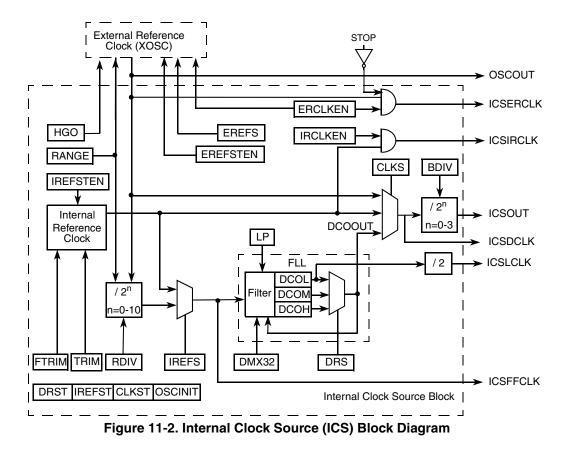

|      | 11.1.2 Block Diagram                  |  |

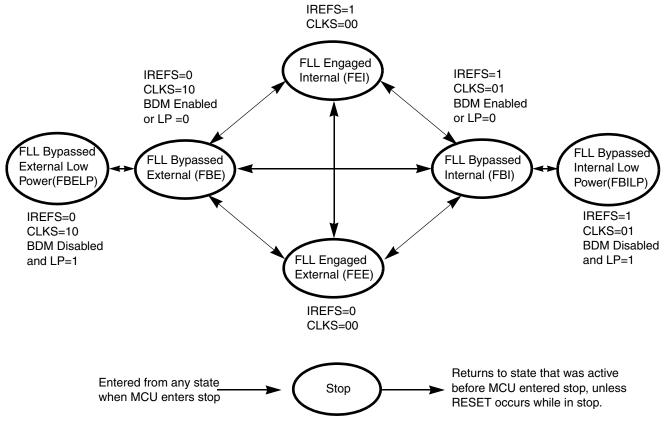

|      | 11.1.3 Modes of Operation             |  |

| 11.2 | External Signal Description           |  |

|      | Register Definition                   |  |

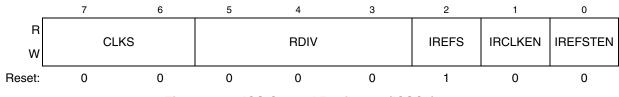

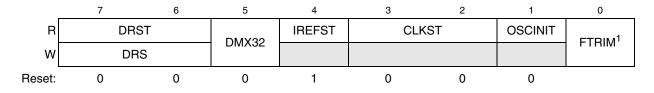

|      | 11.3.1 ICS Control Register 1 (ICSC1) |  |

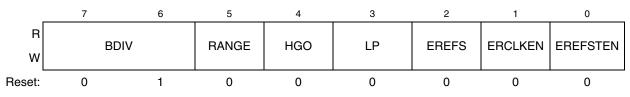

|      | 11.3.2 ICS Control Register 2 (ICSC2) |  |

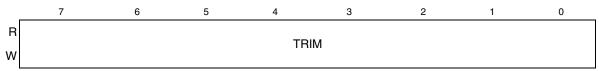

|      | 11.3.3 ICS Trim Register (ICSTRM)     |  |

|      |                                       |  |

### Title

### Page

|      | 11.3.4 ICS Status and Control (ICSSC)                   |  |

|------|---------------------------------------------------------|--|

| 11.4 | Functional Description                                  |  |

|      | 11.4.1 Operational Modes                                |  |

|      | 11.4.2 Mode Switching                                   |  |

|      | 11.4.3 Bus Frequency Divider                            |  |

|      | 11.4.4 Low Power Bit Usage                              |  |

|      | 11.4.5 DCO Maximum Frequency with 32.768 kHz Oscillator |  |

|      | 11.4.6 Internal Reference Clock                         |  |

|      | 11.4.7 External Reference Clock                         |  |

|      | 11.4.8 Fixed Frequency Clock                            |  |

|      | 11.4.9 Local Clock                                      |  |

# Chapter 12 Inter-Integrated Circuit (S08IICV2)

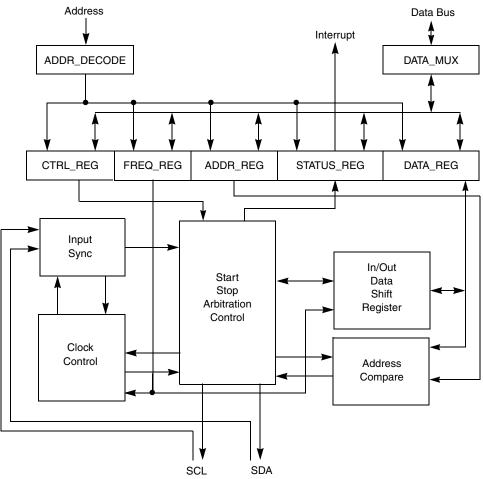

| 12.1 | Introduction                                  |     |

|------|-----------------------------------------------|-----|

|      | 12.1.1 Module Configuration                   |     |

|      | 12.1.2 IIC Clock Gating                       | 241 |

|      | 12.1.3 Features                               |     |

|      | 12.1.4 Modes of Operation                     |     |

|      | 12.1.5 Block Diagram                          |     |

| 12.2 | External Signal Description                   |     |

|      | 12.2.1 SCL — Serial Clock Line                |     |

|      | 12.2.2 SDA — Serial Data Line                 |     |

| 12.3 | Register Definition                           |     |

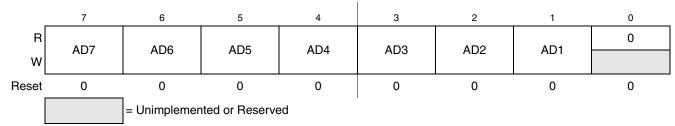

|      | 12.3.1 IIC Address Register (IICxA)           | 245 |

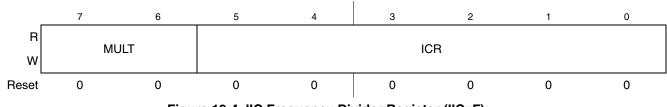

|      | 12.3.2 IIC Frequency Divider Register (IICxF) |     |

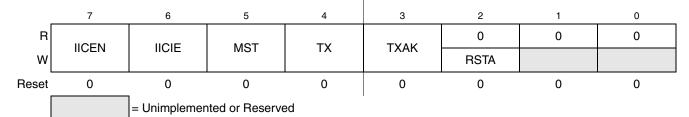

|      | 12.3.3 IIC Control Register (IICxC1)          |     |

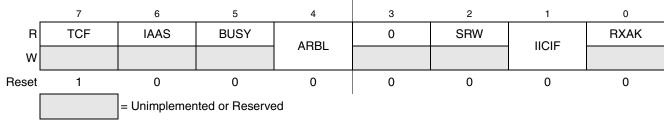

|      | 12.3.4 IIC Status Register (IICxS)            |     |

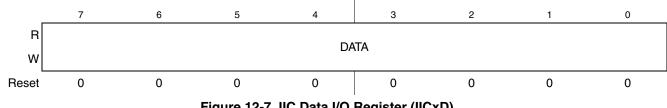

|      | 12.3.5 IIC Data I/O Register (IICxD)          | 249 |

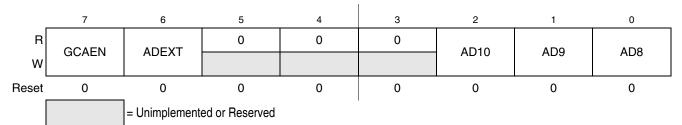

|      | 12.3.6 IIC Control Register 2 (IICxC2)        |     |

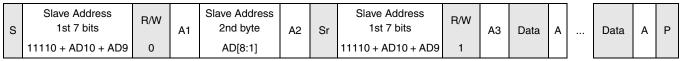

| 12.4 | Functional Description                        | 251 |

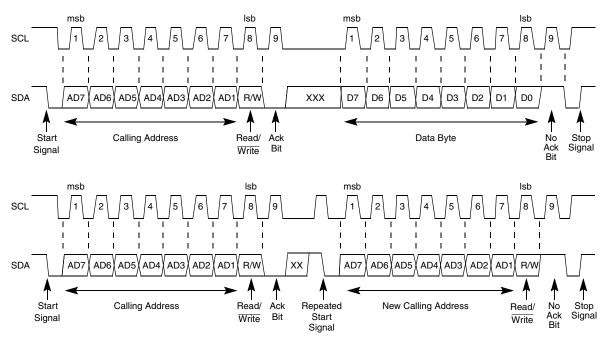

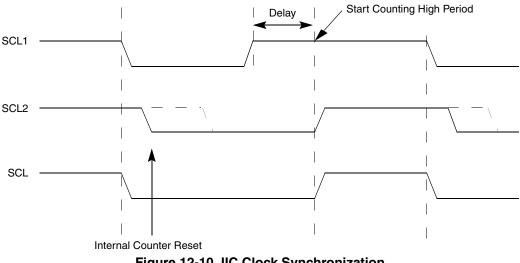

|      | 12.4.1 IIC Protocol                           | 251 |

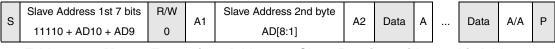

|      | 12.4.2 10-bit Address                         |     |

|      | 12.4.3 General Call Address                   |     |

| 12.5 | Resets                                        |     |

| 12.6 | Interrupts                                    |     |

|      | 12.6.1 Byte Transfer Interrupt                |     |

|      | 12.6.2 Address Detect Interrupt               |     |

|      | 12.6.3 Arbitration Lost Interrupt             |     |

| 12.7 | Initialization/Application Information        |     |

### Title

Page

# Chapter 13 Serial Communications Interface (S08SCIV4)

| 13.1 | Introduc | tion                                       | 259 |

|------|----------|--------------------------------------------|-----|

|      | 13.1.1   | Module Instances                           | 259 |

|      | 13.1.2   | Module Configuration                       | 259 |

|      | 13.1.3   | SCI Clock Gating                           | 259 |

|      |          | Features                                   |     |

|      | 13.1.5   | Modes of Operation                         | 261 |

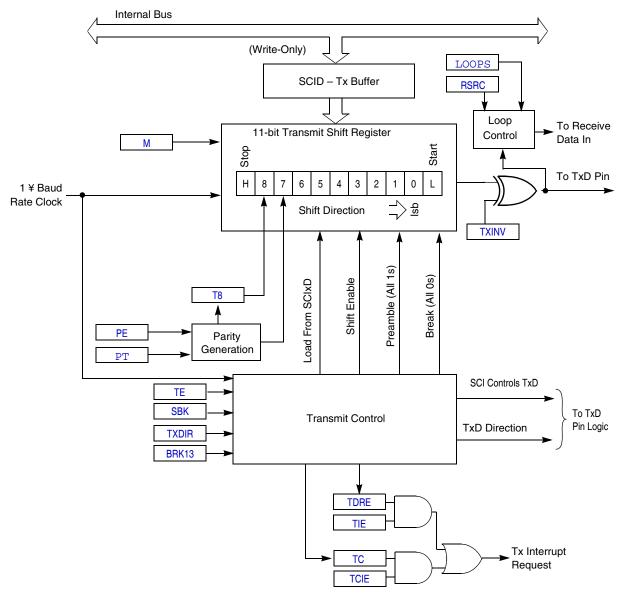

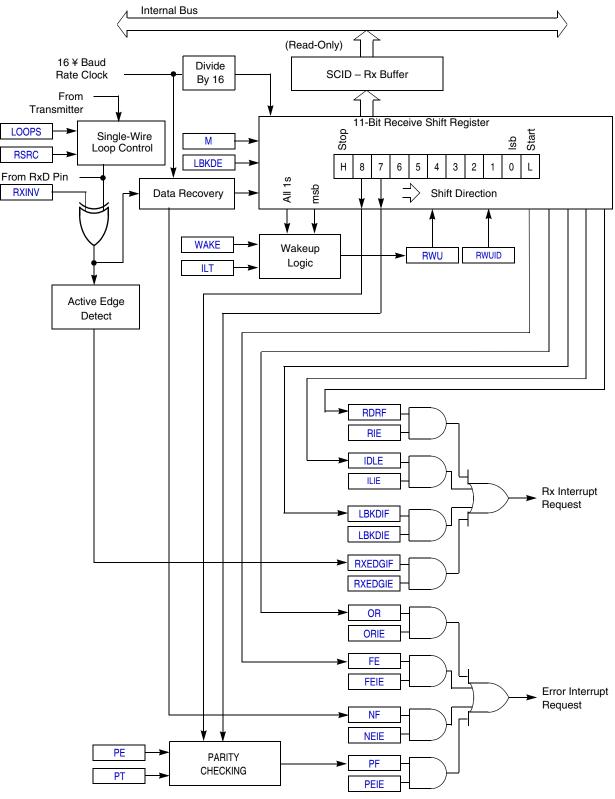

|      | 13.1.6   | Block Diagram                              | 262 |

| 13.2 | Register | Definition                                 | 264 |

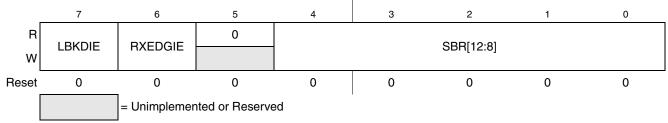

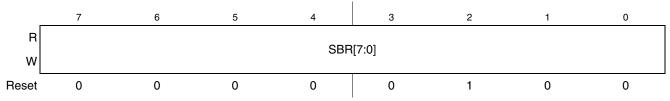

|      | 13.2.1   | SCI Baud Rate Registers (SCIxBDH, SCIxBDL) | 264 |

|      | 13.2.2   | SCI Control Register 1 (SCIxC1)            | 265 |

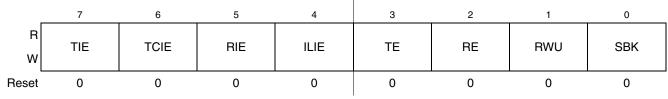

|      | 13.2.3   | SCI Control Register 2 (SCIxC2)            | 266 |

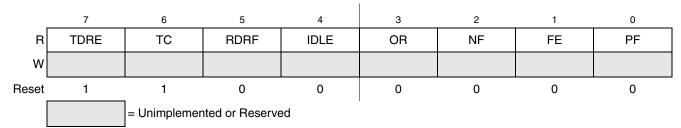

|      | 13.2.4   | SCI Status Register 1 (SCIxS1)             | 267 |

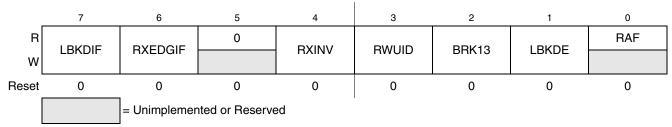

|      | 13.2.5   | SCI Status Register 2 (SCIxS2)             | 269 |

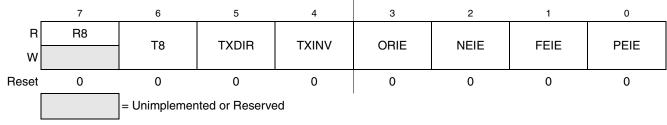

|      | 13.2.6   | SCI Control Register 3 (SCIxC3)            | 270 |

|      | 13.2.7   | SCI Data Register (SCIxD)                  | 271 |

| 13.3 | Function | nal Description                            | 271 |

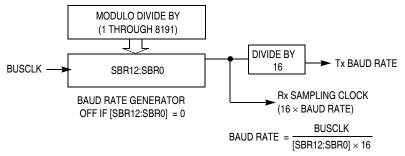

|      | 13.3.1   | Baud Rate Generation                       | 271 |

|      | 13.3.2   | Transmitter Functional Description         | 272 |

|      | 13.3.3   | Receiver Functional Description            | 273 |

|      | 13.3.4   | Interrupts and Status Flags                | 275 |

|      | 13.3.5   | Additional SCI Functions                   | 276 |

### Chapter 14 Serial Peripheral Interface (S08SPIV4)

| 14.1 | Introduction                                 |  |

|------|----------------------------------------------|--|

|      | 14.1.1 Module Configuration                  |  |

|      | 14.1.2 SPI Clock Gating                      |  |

|      | 14.1.3 Features                              |  |

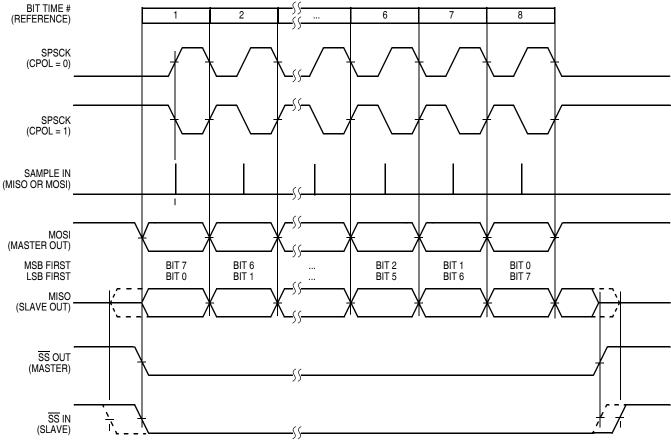

|      | 14.1.4 Block Diagrams                        |  |

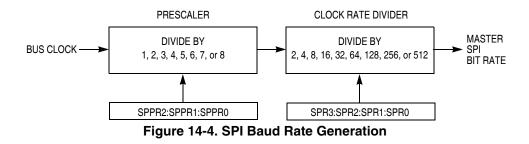

|      | 14.1.5 SPI Baud Rate Generation              |  |

| 14.2 | External Signal Description                  |  |

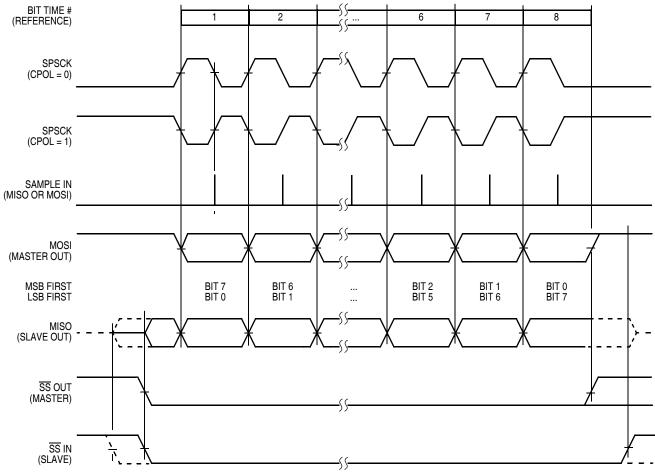

|      | 14.2.1 SPSCK — SPI Serial Clock              |  |

|      | 14.2.2 MOSI — Master Data Out, Slave Data In |  |

|      | 14.2.3 MISO — Master Data In, Slave Data Out |  |

|      | 14.2.4 $\overline{SS}$ — Slave Select        |  |

| 14.3 | Modes of Operation                           |  |

|      | 14.3.1 SPI in Stop Modes                     |  |

| 14.4 | Register Definition                          |  |

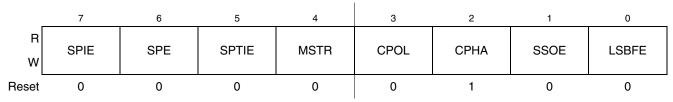

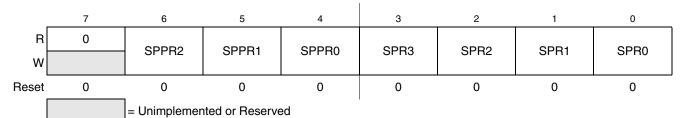

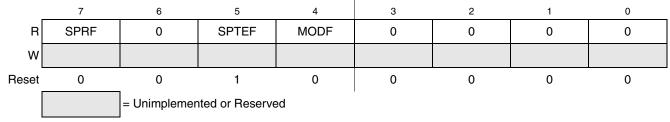

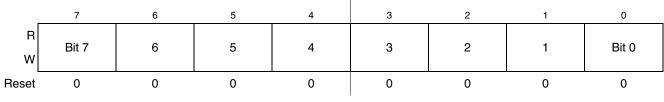

|      | 14.4.1 SPI Control Register 1 (SPIxC1)       |  |

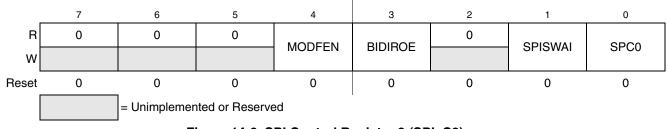

|      | 14.4.2 SPI Control Register 2 (SPIxC2)       |  |

### Title

### Page

|      | 14.4.3   | SPI Baud Rate Register (SPIxBR) | 286 |

|------|----------|---------------------------------|-----|

|      |          | SPI Status Register (SPIxS)     |     |

|      | 14.4.5   | SPI Data Register (SPIxD)       | 288 |

| 14.5 | Function | nal Description                 | 289 |

|      | 14.5.1   | Master Mode                     | 289 |

|      | 14.5.2   | Slave Mode                      | 290 |

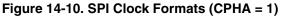

|      | 14.5.3   | SPI Clock Formats               | 291 |

|      | 14.5.4   | Special Features                | 293 |

|      | 14.5.5   | SPI Interrupts                  | 295 |

|      | 14.5.6   | Mode Fault Detection            | 295 |

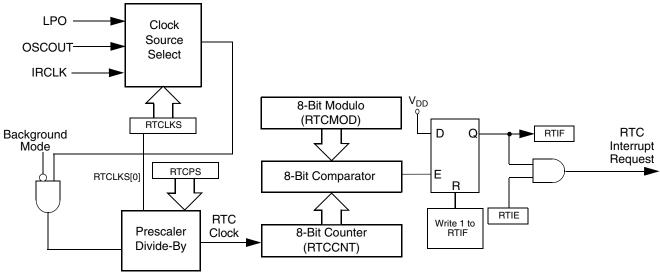

## Chapter 15 Real-Time Counter (S08RTCV1)

| 15.1 | Introduction                                   |  |

|------|------------------------------------------------|--|

|      | 15.1.1 RTC Clock Gating                        |  |

|      | 15.1.2 Features                                |  |

|      | 15.1.3 Modes of Operation                      |  |

|      | 15.1.4 Block Diagram                           |  |

| 15.2 | External Signal Description                    |  |

| 15.3 | Register Definition                            |  |

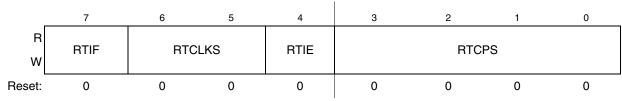

|      | 15.3.1 RTC Status and Control Register (RTCSC) |  |

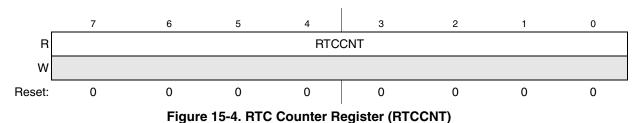

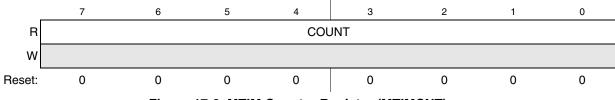

|      | 15.3.2 RTC Counter Register (RTCCNT)           |  |

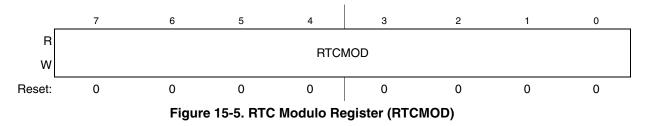

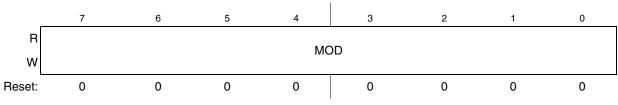

|      | 15.3.3 RTC Modulo Register (RTCMOD)            |  |

| 15.4 | Functional Description                         |  |

|      | 15.4.1 RTC Operation Example                   |  |

| 15.5 | Initialization/Application Information         |  |

|      |                                                |  |

### Chapter 16 Timer/Pulse-Width Modulator (S08TPMV3)

| 16.1 | Introduction                                     |  |

|------|--------------------------------------------------|--|

|      | 16.1.1 TPM External Clock                        |  |

|      | 16.1.2 Module Instances                          |  |

|      | 16.1.3 Module Configuration                      |  |

|      | 16.1.4 TPM Clock Gating                          |  |

|      | 16.1.5 Features                                  |  |

|      | 16.1.6 Modes of Operation                        |  |

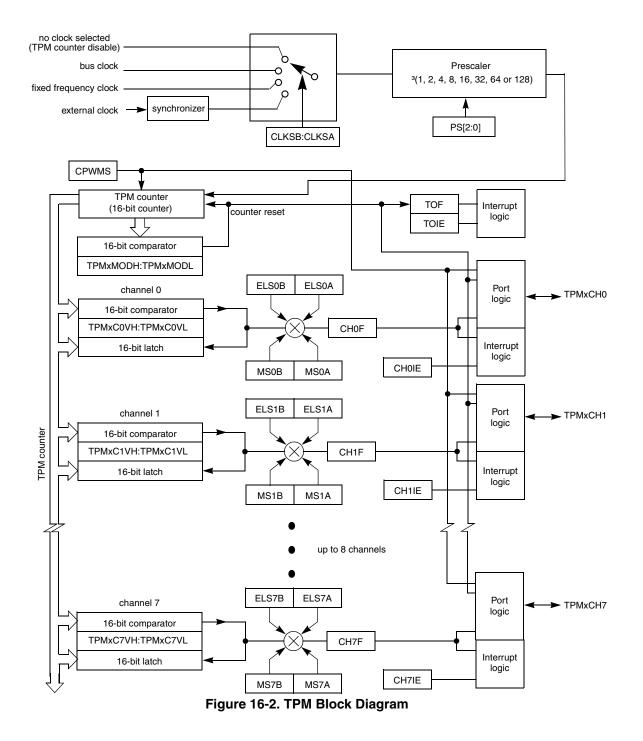

|      | 16.1.7 Block Diagram                             |  |

| 16.2 | Signal Description                               |  |

|      | 16.2.1 Detailed Signal Descriptions              |  |

| 16.3 | Register Definition                              |  |

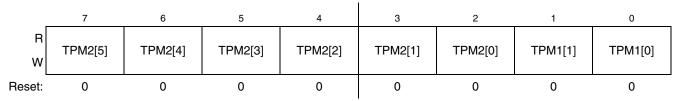

|      | 16.3.1 TPM Status and Control Register (TPMxSC)  |  |

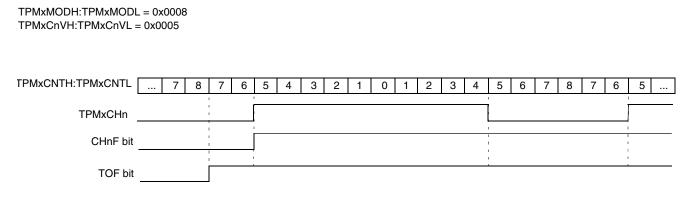

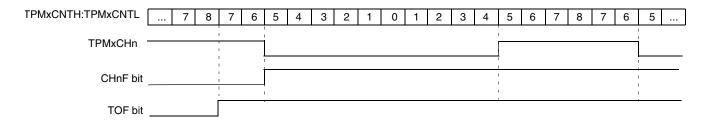

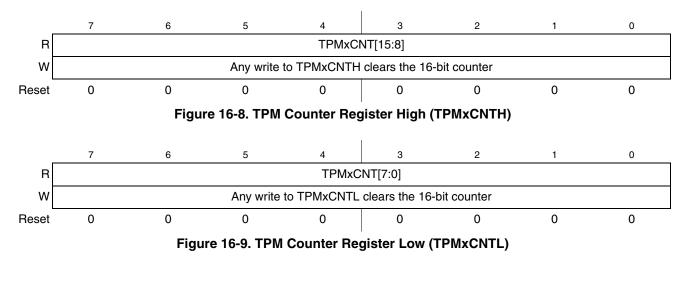

|      | 16.3.2 TPM-Counter Registers (TPMxCNTH:TPMxCNTL) |  |

|      |                                                  |  |

### Title

### Page

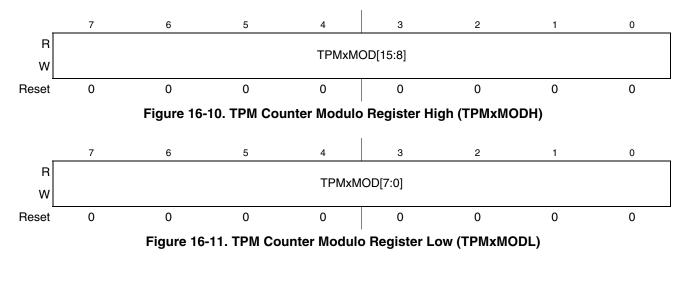

|      | 16.3.3 TPM Counter Modulo Registers (TPMxMODH:TPMxMODL)     |  |

|------|-------------------------------------------------------------|--|

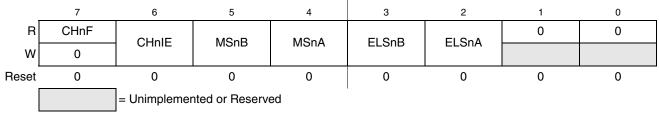

|      | 16.3.4 TPM Channel n Status and Control Register (TPMxCnSC) |  |

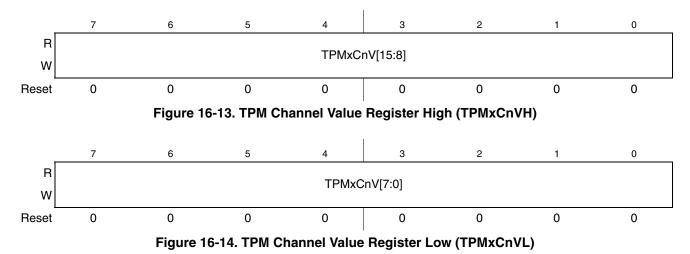

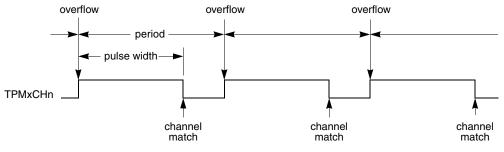

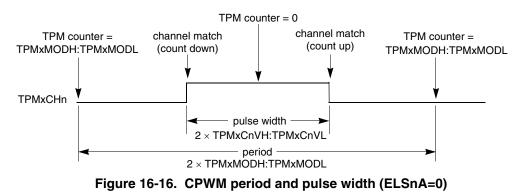

|      | 16.3.5 TPM Channel Value Registers (TPMxCnVH:TPMxCnVL)      |  |

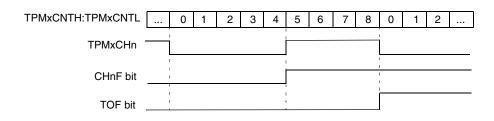

| 16.4 | Functional Description                                      |  |

|      | 16.4.1 Counter                                              |  |

|      | 16.4.2 Channel Mode Selection                               |  |

| 16.5 | Reset Overview                                              |  |

|      | 16.5.1 General                                              |  |

|      | 16.5.2 Description of Reset Operation                       |  |

| 16.6 | Interrupts                                                  |  |

|      | 16.6.1 General                                              |  |

|      | 16.6.2 Description of Interrupt Operation                   |  |

# Chapter 17 Modulo Timer (S08MTIMV1)

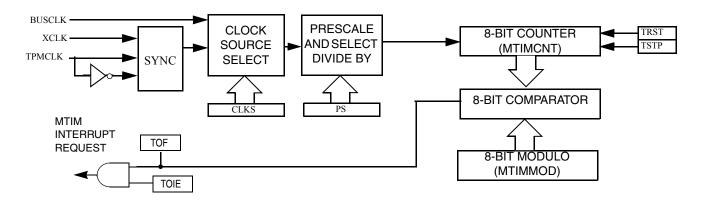

| 17.1 | Introduction                         |  |

|------|--------------------------------------|--|

|      | 17.1.1 MTIM Clock Gating             |  |

|      | 17.1.2 Features                      |  |

|      | 17.1.3 Modes of Operation            |  |

|      | 17.1.4 Block Diagram                 |  |

| 17.2 | External Signal Description          |  |

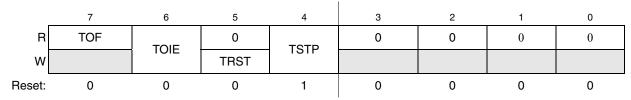

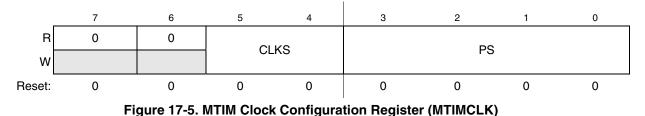

| 17.3 | Memory Map and Register Definition   |  |

|      | 17.3.1 Memory Map (Register Summary) |  |

|      | 17.3.2 Register Descriptions         |  |

| 17.4 | Functional Description               |  |

|      | 17.4.1 MTIM Operation Example        |  |

## Chapter 18 Development Support

| Introduction                                                |                                                                                                                                                            |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                             |                                                                                                                                                            |

| 18.1.2 Module Configuration                                 |                                                                                                                                                            |

| 18.1.3 Features                                             |                                                                                                                                                            |

| Background Debug Controller (BDC)                           |                                                                                                                                                            |

| 18.2.1 BKGD Pin Description                                 |                                                                                                                                                            |

| 18.2.2 Communication Details                                |                                                                                                                                                            |

| 18.2.3 BDC Commands                                         |                                                                                                                                                            |

| 18.2.4 BDC Hardware Breakpoint                              |                                                                                                                                                            |

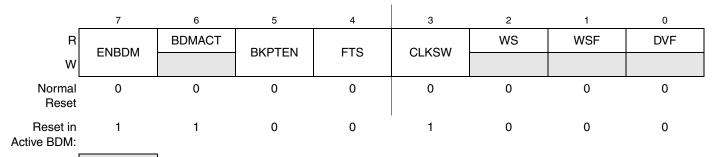

| Register Definition                                         |                                                                                                                                                            |

| 18.3.1 BDC Registers and Control Bits                       |                                                                                                                                                            |

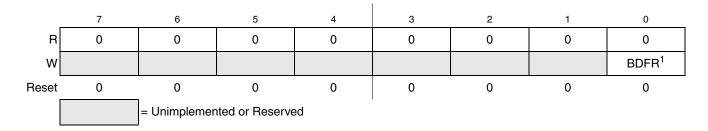

| 18.3.2 System Background Debug Force Reset Register (SBDFR) |                                                                                                                                                            |

|                                                             | <ul> <li>18.2.1 BKGD Pin Description</li> <li>18.2.2 Communication Details</li> <li>18.2.3 BDC Commands</li> <li>18.2.4 BDC Hardware Breakpoint</li> </ul> |

### Title

### Page

# Chapter 19 Debug Module (DBG) (64K)

| Introduction                       |                                                                                                                                                                                                                                                                                                                         |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19.1.1 Features                    |                                                                                                                                                                                                                                                                                                                         |

| 19.1.2 Modes of Operation          |                                                                                                                                                                                                                                                                                                                         |

|                                    |                                                                                                                                                                                                                                                                                                                         |

|                                    |                                                                                                                                                                                                                                                                                                                         |

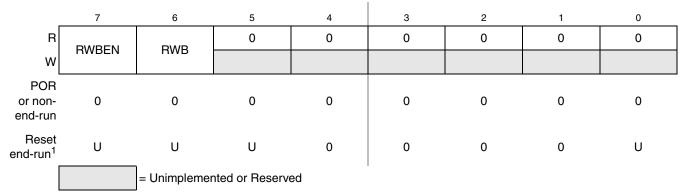

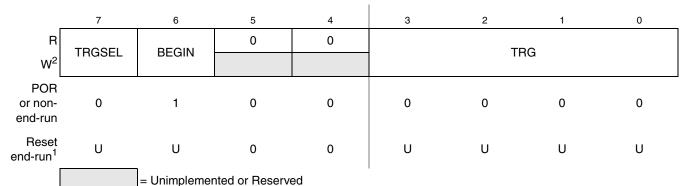

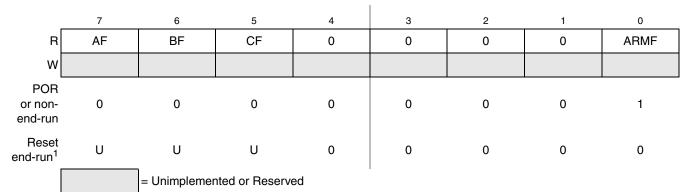

| Memory Map and Registers           |                                                                                                                                                                                                                                                                                                                         |

| 19.3.1 Module Memory Map           |                                                                                                                                                                                                                                                                                                                         |

| 19.3.2 Register Descriptions       |                                                                                                                                                                                                                                                                                                                         |

|                                    |                                                                                                                                                                                                                                                                                                                         |

|                                    |                                                                                                                                                                                                                                                                                                                         |

|                                    |                                                                                                                                                                                                                                                                                                                         |

| 19.4.3 Trigger Selection           |                                                                                                                                                                                                                                                                                                                         |

| 19.4.4 Trigger Break Control (TBC) |                                                                                                                                                                                                                                                                                                                         |

|                                    |                                                                                                                                                                                                                                                                                                                         |

| 19.4.6 Interrupt Priority          |                                                                                                                                                                                                                                                                                                                         |

| Resets                             |                                                                                                                                                                                                                                                                                                                         |

| Interrupts                         |                                                                                                                                                                                                                                                                                                                         |

|                                    | 19.1.1 Features19.1.2 Modes of Operation19.1.3 Block DiagramSignal DescriptionMemory Map and Registers19.3.1 Module Memory Map19.3.2 Register DescriptionsFunctional Description19.4.1 Comparator19.4.2 Breakpoints19.4.3 Trigger Selection19.4.4 Trigger Break Control (TBC)19.4.5 FIFO19.4.6 Interrupt PriorityResets |

# Chapter 1 Device Overview

The MC9S08LG32 and MC9S08LG16 are the members of the low-cost, low-power, and high-performance HCS08 family of 8-bit microcontroller units (MCUs). All MCUs in the family use the enhanced HCS08 core and are available with a variety of memory sizes and package types.

The MC9S08LG32 series MCUs are targeted to serve automotive, consumer and industrial markets. Please check the ordering part numbers for different qualification tier products in *Ordering Information section of MC9S08LG32 Data Sheet*.

# 1.1 Devices in the MC9S08LG32 Series

Table 1-1 summarizes the feature set available in the MC9S08LG32 series of MCUs.

| Feature            | MC9S08LG32       |                  |                  | MC9S08LG16       |                  |  |

|--------------------|------------------|------------------|------------------|------------------|------------------|--|

| Flash size (bytes) | 32,768           |                  |                  | 18,432           |                  |  |

| RAM size (bytes)   |                  |                  | 1984             |                  |                  |  |

| Pin quantity       | 80               | 64               | 48               | 64               | 48               |  |

| ADC                | 16 ch            | 12 ch            | 9 ch             | 12 ch            | 9 ch             |  |

| LCD                | 8 x 37<br>4 x 41 | 8 x 29<br>4 x 33 | 8 x 21<br>4 x 25 | 8 x 29<br>4 x 33 | 8 x 21<br>4 x 25 |  |

| ICE + DBG          | yes              |                  |                  |                  |                  |  |

| ICS                | yes              |                  |                  |                  |                  |  |

| IIC                | yes              |                  |                  |                  |                  |  |

| IRQ                | yes              |                  |                  |                  |                  |  |

| КВІ                | 8 pin            |                  |                  |                  |                  |  |

| GPIOs              | 69               | 53               | 39               | 53               | 39               |  |

| RTC                | yes              |                  |                  |                  |                  |  |

| МТІМ               |                  |                  | yes              |                  |                  |  |

| SCI1               |                  |                  | yes              |                  |                  |  |

| SCI2               |                  |                  | yes              |                  |                  |  |

| SPI                |                  |                  | yes              |                  |                  |  |

| TPM1 channels      | 2                |                  |                  |                  |                  |  |

| TPM2 channels      | 6                |                  |                  |                  |                  |  |

| XOSC               | yes              |                  |                  |                  |                  |  |

Table 1-1. MC9S08LG32 series Features by MCU and Package

**Chapter 1 Device Overview**

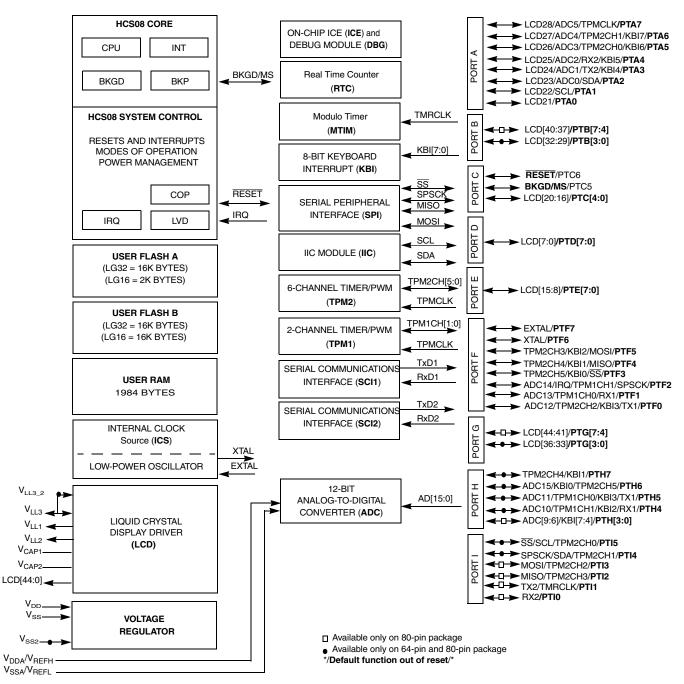

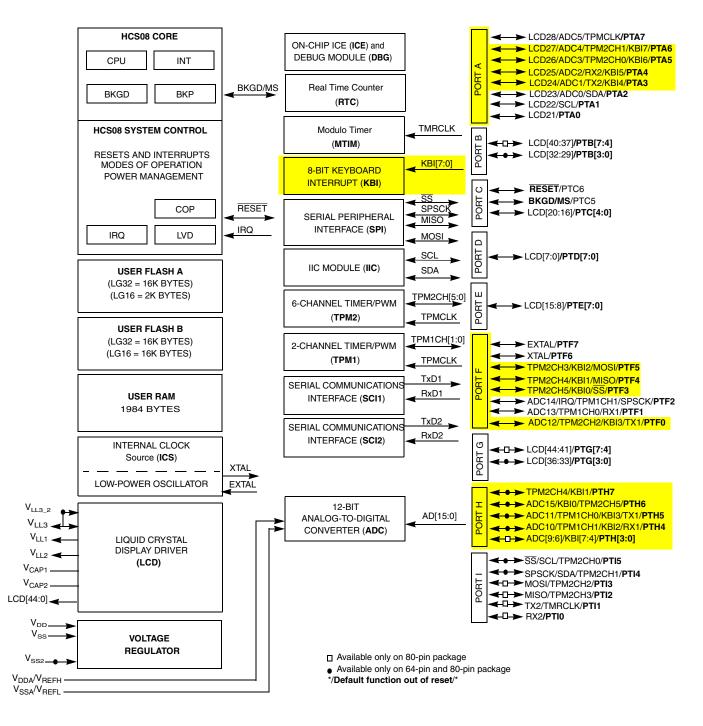

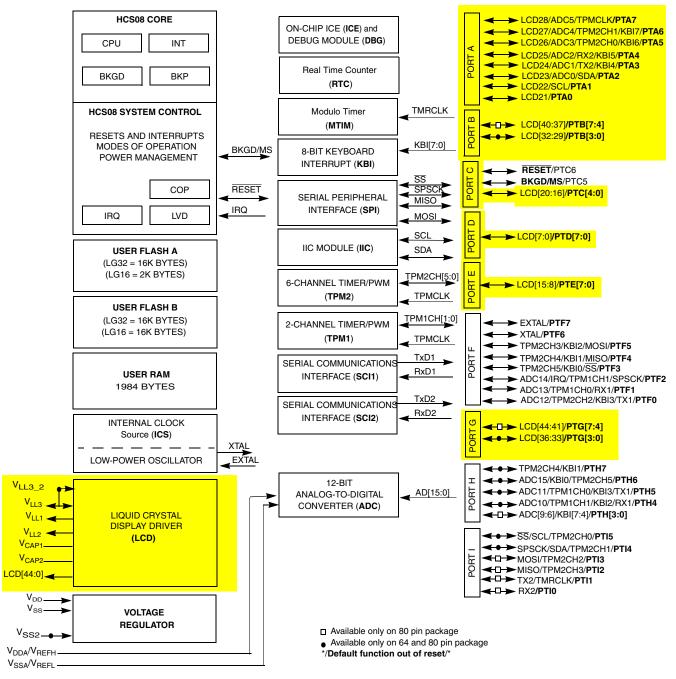

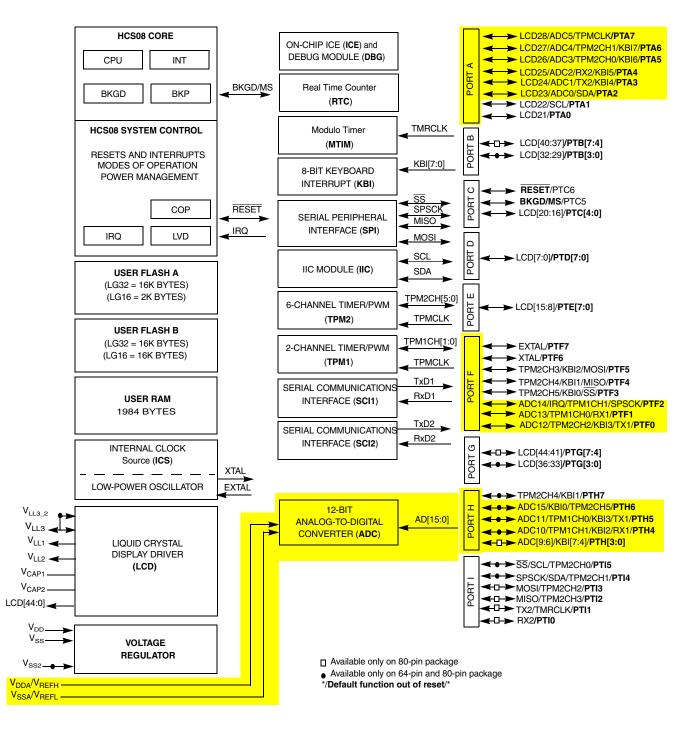

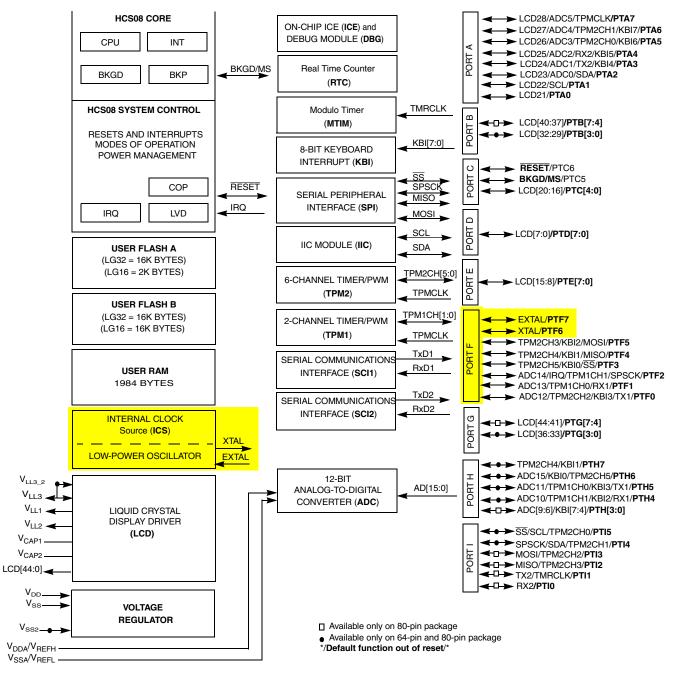

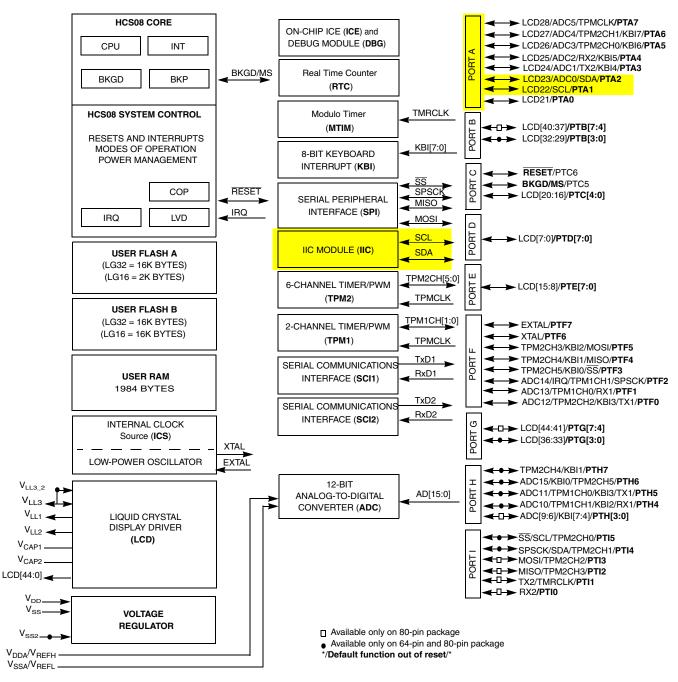

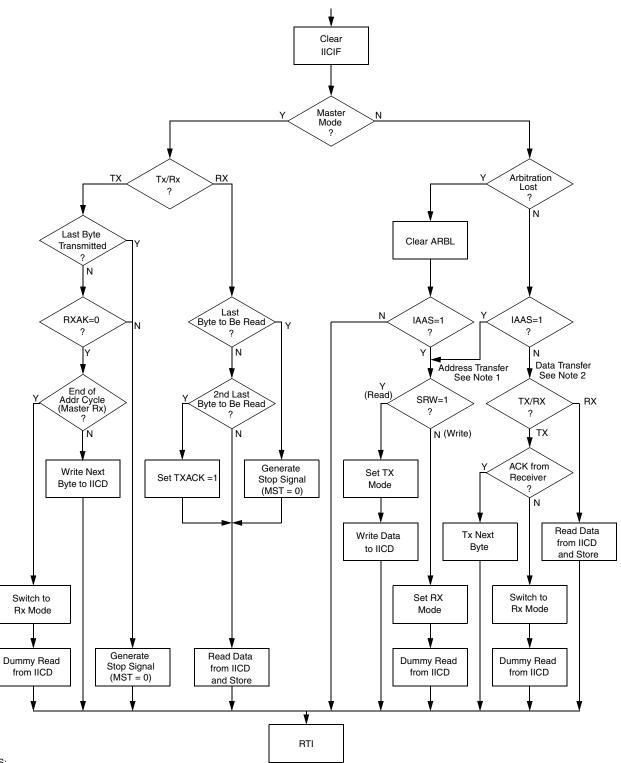

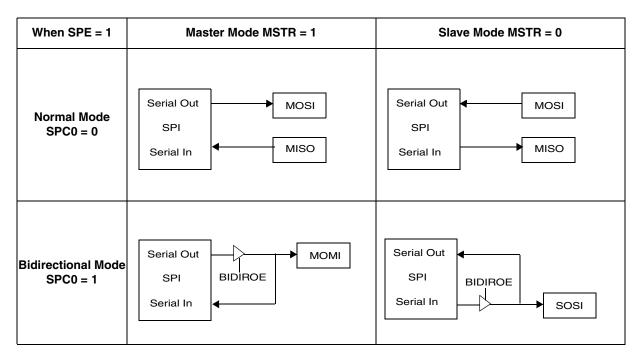

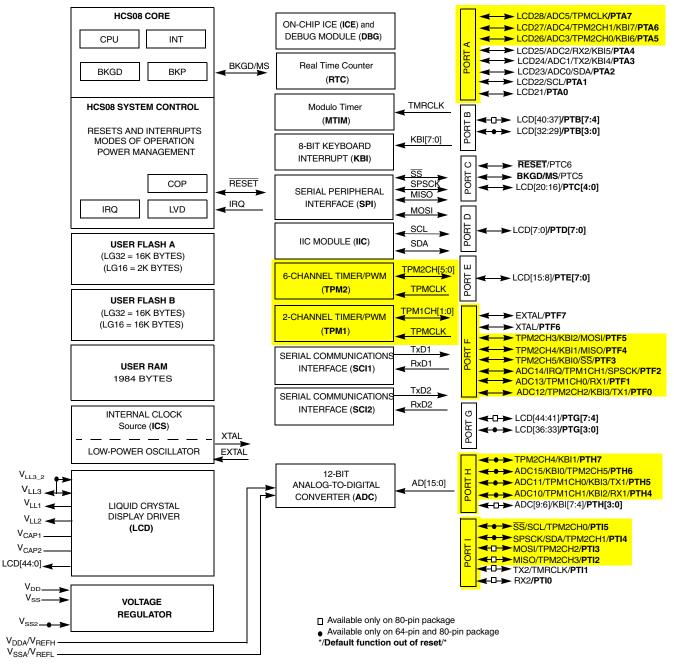

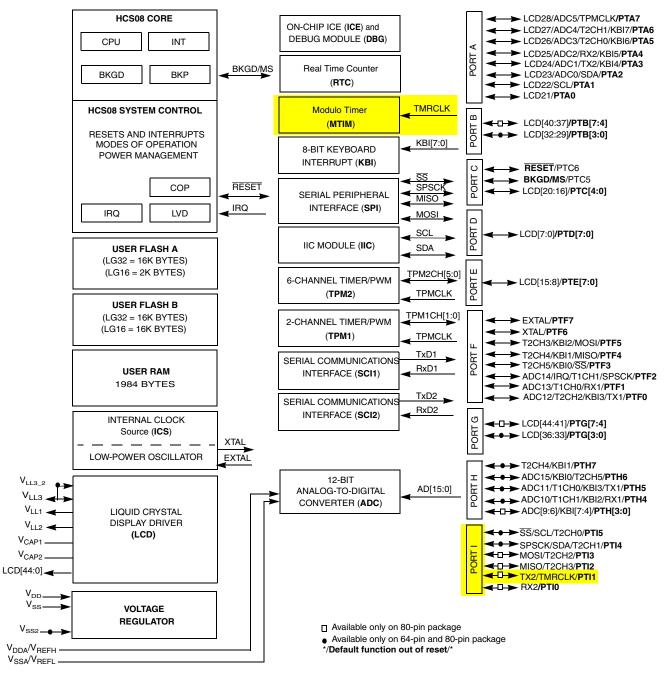

# 1.2 MCU Block Diagram

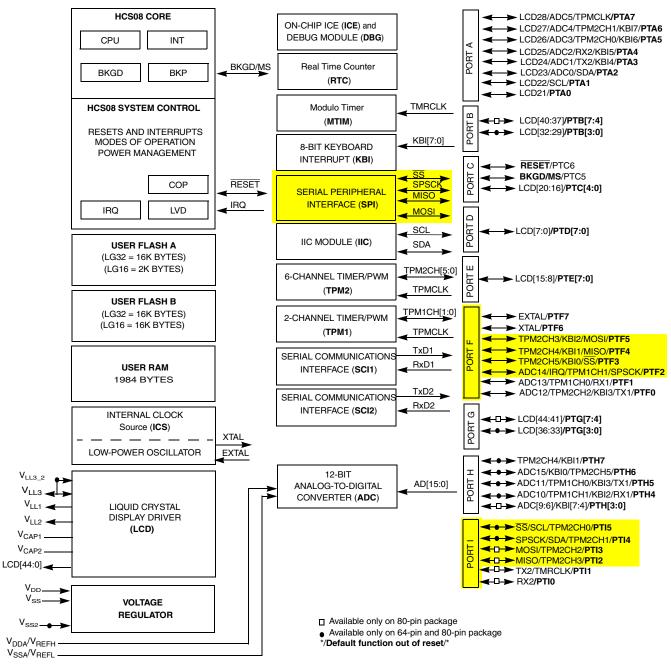

The block diagram in Figure 1-1 shows the structure of the MC9S08LG32 series MCU.

Figure 1-1. MC9S08LG32 Series Block Diagram

#### **Chapter 1 Device Overview**

#### Table 1-2 provides the functional version of the on-chip modules.

| Module                            | Version |   |

|-----------------------------------|---------|---|

| Analog-to-Digital Converter       | (ADC12) | 1 |

| Central Processor Unit            | (CPU)   | 5 |

| Inter-Integrated Circuit          | (IIC)   | 2 |

| Internal Clock Source             | (ICS)   | 3 |

| Keyboard Interrupt                | (KBI)   | 2 |

| Liquid Crystal Display Module     | (LCD)   | 1 |

| Low Power Oscillator              | (XOSC)  | 1 |

| Modulo Timer                      | (MTIM)  | 1 |

| On-Chip In-Circuit Debug/Emulator | (DBG)   | 3 |

| Real Time Counter                 | (RTC)   | 1 |

| Serial Communications Interface   | (SCI)   | 4 |

| Serial Peripheral Interface       | (SPI)   | 4 |

| Timer Pulse Width Modulator       | (TPM)   | 3 |

#### Table 1-2. Module Versions

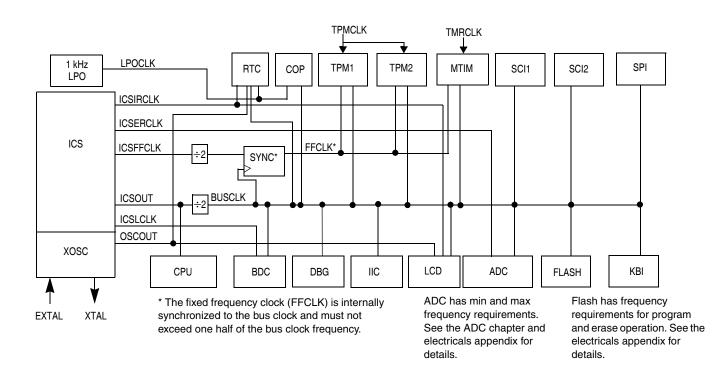

# **1.3 System Clock Distribution**

Figure 1-2 shows a simplified clock connection diagram of the ICS. Some modules in the MCU have selectable clock inputs as shown. The clock inputs to the modules indicate the clock(s) that are used to drive the module function. All memory-mapped registers associated with the modules are clocked with BUSCLK. The ICS supplies the following clock sources:

- ICSOUT This clock source is used as the CPU clock and is divided by 2 to generate the peripheral bus clock, BUSCLK. Control bits in the ICS control registers determine which of the three clock sources is connected:

- Internal reference clock

- External reference clock

- Frequency-locked loop (FLL) output

For more information on configuring the ICSOUT clock, see Chapter 11, "Internal Clock Source (S08ICSV3)."

- ICSLCLK This clock source is derived from the digitally controlled oscillator (DCO) of the ICS when the ICS is configured to run off the internal or external reference clock. The development tools can select this internal self-clocked source (~ 8 MHz) to speed up the BDC communications in systems where the bus clock is slow.

- ICSERCLK This is an external reference clock and can be selected as the alternate clock for ADC. The "Optional External Reference Clock" section in Chapter 11, "Internal Clock Source (S08ICSV3)," explains the ICSERCLK in more detail. For more information regarding the use of ICSERCLK with this module, see Chapter 10, "Analog-to-Digital Converter (S08ADC12V1)."

- ICSIRCLK This is an internal reference clock and can be selected as the RTC clock source, or as ALTCLK source for the LCD. Chapter 11, "Internal Clock Source (S08ICSV3)" explains the ICSIRCLK in more detail. For more information regarding use of ICSIRCLK with these modules, see Chapter 15, "Real-Time Counter (S08RTCV1)," and Chapter 9, "LCD Module (S08LCDLPV1)."

- ICSFFCLK This fixed frequency clock (FFCLK) is generated after it is synchronized with the bus clock. The frequency of the ICSFFCLK is determined by the settings of the ICS. For more information, see the "Fixed Frequency Clock" section in Chapter 11, "Internal Clock Source (S08ICSV3)." It can be selected as a clock source for the MTIM and TPM modules. For information regarding use of ICSFFCLK with these modules, see Chapter 16, "Timer/Pulse-Width Modulator (S08TPMV3)," and Chapter 17, "Modulo Timer (S08MTIMV1)."

- LPOCLK This clock is generated from an internal low power oscillator (LPO) that is completely independent of the ICS module. The LPOCLK can be selected as the clock source to the COP and RTC module. See Section 5.4, "Computer Operating Properly (COP) Watchdog," and Chapter 15, "Real-Time Counter (S08RTCV1)," for details on using the LPOCLK with these modules.

- OSCOUT This is the output of the XOSC module and can be selected as the LCD and RTC clock source. This clock source can be used for LCD and RTC in stop2 mode. For more information regarding use of OSCOUT with these modules, see Chapter 15, "Real-Time Counter (S08RTCV1)," and Chapter 9, "LCD Module (S08LCDLPV1)."

- TPMCLK The TPMCLK is an optional external clock source for the TPM modules. The TPMCLK must be limited to 1/4th of the frequency of the bus clock for synchronization. For more information, see the "External TPM Clock Sources" section in Chapter 16, "Timer/Pulse-Width Modulator (S08TPMV3)."

- TMRCLK The TMRCLK is an optional external clock source for the MTIM module. For more information, see Chapter 17, "Modulo Timer (S08MTIMV1)."

#### **NOTE** ICSERCLK is a gated version of OSCOUT. ICSERCLK is not available in STOP modes while OSCOUT is available if ERCLKEN and EREFSTEN are set.

Figure 1-2. System Clock Distribution Diagram

**Chapter 1 Device Overview**

# Chapter 2 Pins and Connections

# 2.1 Introduction

This section describes signals that connect to the package pins. It includes pinout diagrams, recommended system connections, and detailed discussions of signals.

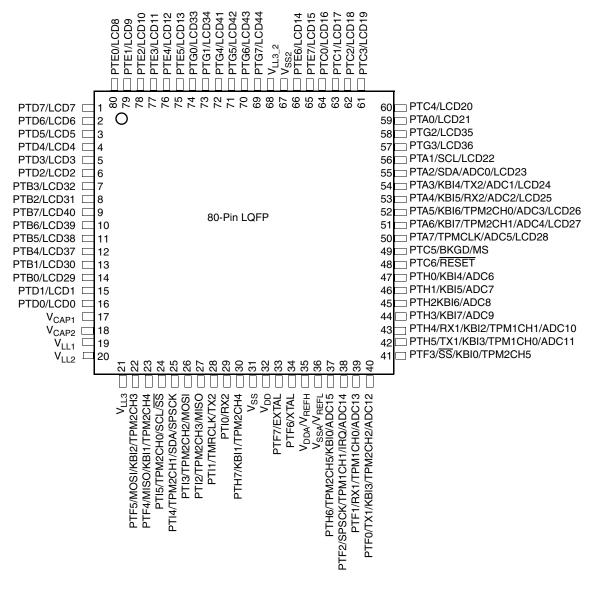

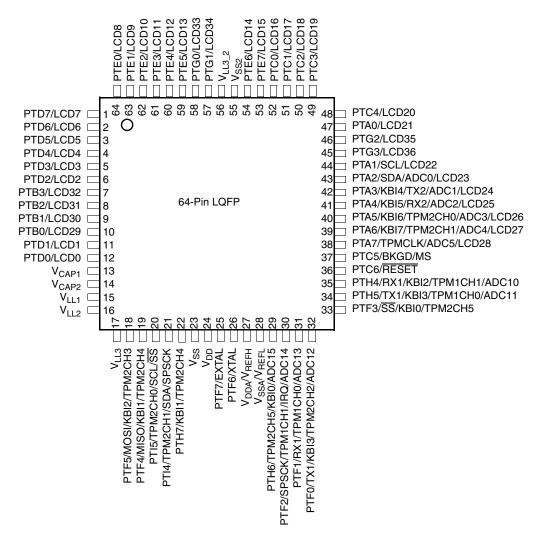

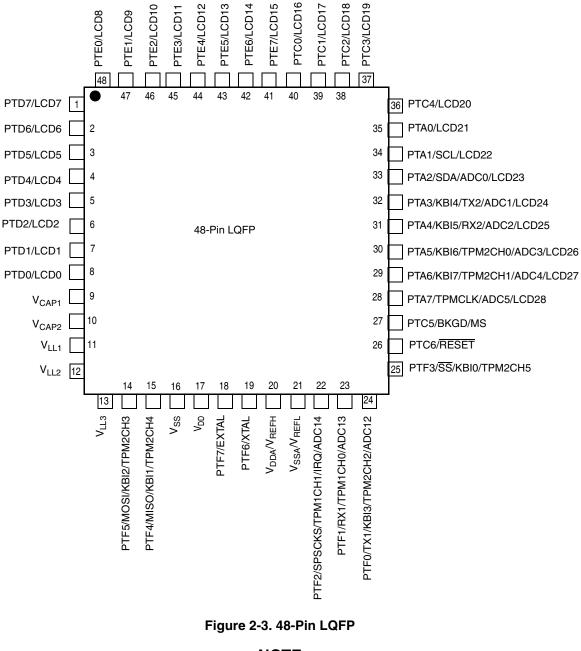

# 2.2 Device Pin Assignment

This section shows the pin assignments for MC9S08LG32 series. The priority of functions on a pin is in ascending order from left to right and bottom to top. Another view of pinouts and function priority is given in Table 2-1.

#### Figure 2-1. 80-Pin LDFP

#### NOTE

$V_{REFH}/V_{REFL}$  are internally connected to  $V_{DDA}/V_{SSA}$ .

Figure 2-2. 64-Pin LQFP

#### NOTE

$V_{REFH}/V_{REFL}$  are internally connected to  $V_{DDA}/V_{SSA}$ .

NOTE

$V_{REFH}/V_{REFL}$  are internally connected to  $V_{DDA}/V_{SSA}$ .

**Chapter 2 Pins and Connections**

# 2.3 Recommended System Connections

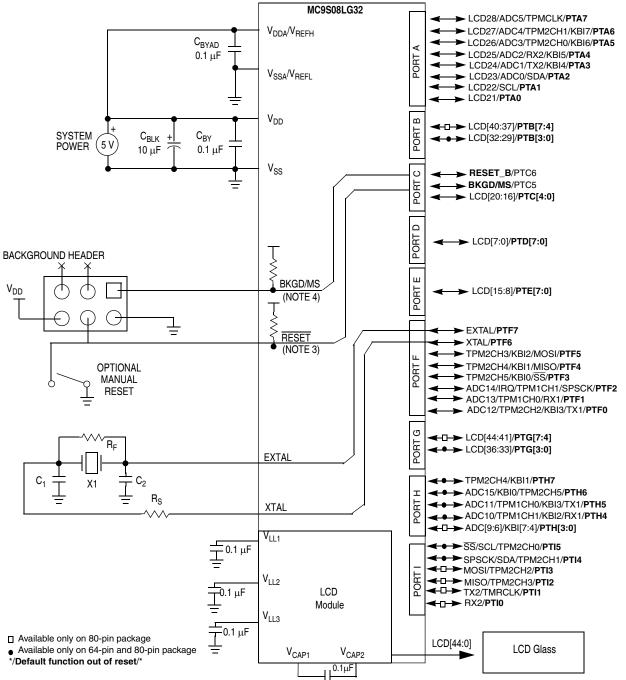

Figure 2-4 shows pin connections that are common to MC9S08LG32 series application systems.

#### NOTES

- <sup>1</sup> RESET pin can only be used to reset into user mode, you can not enter BDM using RESET pin. To enter BDM, hold MS low during POR or write a 1 to BDFR in SBDFR with MS low after issuing BDM command.

- <sup>2</sup> RC filter on RESET pin recommended for noisy environments.

- <sup>3</sup> When PTC6 is configured as RESET, pin becomes bi-directional with output being open-drain drive containing an internal pullup device.

- <sup>4</sup> When PTC5 is configured as BKGD, pin becomes bi-directional.

- <sup>5</sup> LCD mode shown is for Charge pump enabled, other configurations are necessary for different LCD modes.

#### Figure 2-4. Basic System Connections

### 2.3.1 Power

$V_{DD}$  and  $V_{SS}$  are primary power supply pins for the MCU. This voltage source supplies power to all I/O buffer circuitry and to an internal voltage regulator. The internal voltage regulator provides a regulated lower-voltage source for the CPU and other internal circuitry of the MCU.

The LCD/GPIO can be powered differently. For additional information, see Chapter 6, "Parallel Input/Output Control."

Typically, application systems have two separate capacitors across the power pins. In this case, there must be a bulk electrolytic capacitor, such as a 10- $\mu$ F tantalum capacitor, to provide bulk charge storage for the overall system, and a 0.1- $\mu$ F ceramic bypass capacitor located as near to the MCU power pins as practical to suppress high-frequency noise.

$V_{\text{DDA}}$  and  $V_{\text{SSA}}$  are the analog power supply pins for the MCU. This voltage source supplies power to the ADC modules.

$V_{REFH}$  and  $V_{REFL}$  pins are the voltage reference high and the voltage reference low inputs, respectively, for the ADC module. For this MCU,  $V_{DDA}$  shares the  $V_{REFH}$  pin and  $V_{SSA}$  shares the  $V_{REFL}$  pin.

### 2.3.2 Oscillator

Immediately after reset, the MCU uses an internally generated clock provided by the internal clock source (ICS) module. The ICS can be configured to run off the on-chip oscillator (ICSERCLK). The output of the oscillator (OSCOUT) is used to run the RTC and LCD bypassing the ICS. The oscillator can be configured to run in stop2 or stop3 modes. For more information, see Section 1.3, "System Clock Distribution," and Chapter 11, "Internal Clock Source (S08ICSV3)."

The oscillator (XOSC) in this MCU is a Pierce oscillator that can accommodate a crystal or ceramic resonator. An external clock source can optionally be connected to the EXTAL input pin.

Refer to Figure 2-4 for the following discussion.  $R_S$  (when used) and  $R_F$  must be low-inductance resistors, such as carbon composition resistors. Wire-wound resistors and some metal film resistors have too much inductance.  $C_1$  and  $C_2$  normally must be high-quality ceramic capacitors that are specifically designed for high-frequency applications.

$R_F$  provides a bias path to keep the EXTAL input in its linear range during crystal startup; its value is not generally critical. Typical systems use 1 M $\Omega$  to 10 M $\Omega$ . Higher values are sensitive to humidity and lower values reduce gain and (in extreme cases) could prevent startup.

$C_1$  and  $C_2$  are typically in the 5 pF to 25 pF range and are chosen to match the requirements of a specific crystal or resonator. Be sure to consider the printed circuit board (PCB) capacitance and the MCU pin capacitance when selecting  $C_1$  and  $C_2$ . The crystal manufacturer typically specifies a load capacitance, which is the series combination of  $C_1$  and  $C_2$  (which are usually of the same size). As a first-order approximation, use 10 pF as an estimate of combined pin and PCB capacitance for each oscillator pin (EXTAL and XTAL).

# 2.3.3 **RESET**

After a power-on reset (POR), the PTC6/RESET pin defaults to RESET. Clearing RSTPE in SOPT1 configures the pin to be an output-only pin with an open-drain drive and an internal pullup device. RSTPE is a write-once bit; so once written, it becomes read-only until the next reset. This bit is sticky and is reset only at POR or LVD; it retains its value across other resets. When enabled, the RESET pin can be used to reset the MCU from an external source when the pin is driven low.

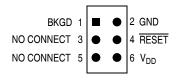

Internal POR and low-voltage reset circuitry typically make external reset circuitry unnecessary. This pin is normally connected to the standard 6-pin background debug connector, so a development system can directly reset the MCU system. A manual external reset can be added by supplying a simple switch to ground (pull reset pin low to force a reset).

Whenever any non-POR reset is initiated (whether from an external signal or from an internal system), the enabled  $\overline{\text{RESET}}$  pin is driven low for about 34 bus cycles. The reset circuitry decodes the cause of reset and records it by setting a corresponding bit in the system reset status register (SRS).

#### NOTE

This pin does not contain a clamp diode to  $V_{\mbox{\scriptsize DD}}$  and must not be driven above  $V_{\mbox{\scriptsize DD}}.$

The voltage on the internally pulled up  $\overline{\text{RESET}}$  pin, when measured, is below  $V_{DD}$ . The internal gates connected to this pin are pulled to  $V_{DD}$ . If the  $\overline{\text{RESET}}$  pin is required to drive to a  $V_{DD}$  level, an external pullup must be used.

In EMC-sensitive applications, an external RC filter is recommended on the  $\overline{\text{RESET}}$  pin, if enabled.

### 2.3.4 Background / Mode Select (BKGD/MS)

During POR or background debug force reset (for more information, see Section 5.8.3, "System Background Debug Force Reset Register (SBDFR)"), the PTC5/BKGD/MS pin functions as a mode select pin. Immediately after any reset, the pin functions as the background pin and can be used for background debug communication. When BKGD/MS function is enabled with BKGDPE = 1, an internal pullup device automatically becomes active. Clearing BKGDPE in SOPT1 configures the pin to be an output-only pin.

The background debug communication function is enabled when BKGDPE in SOPT1 is set. BKGDPE is set following any reset of the MCU and must be cleared to use the PTC5/BKGD/MS pin's alternative pin functions.

After any reset, if nothing is connected to this pin, the MCU enters normal operating mode. If a debug system is connected to the 6-pin standard background debug header, it can hold BKGD/MS low. It can do this during a POR or after issuing a background debug force reset. This forces the MCU to active background mode.

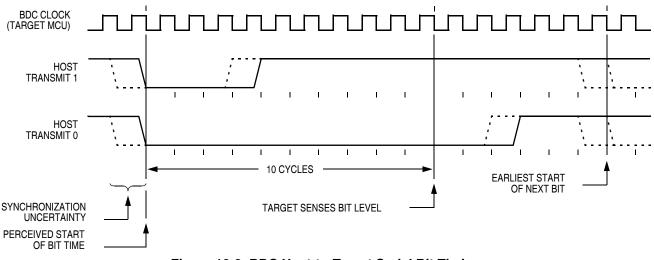

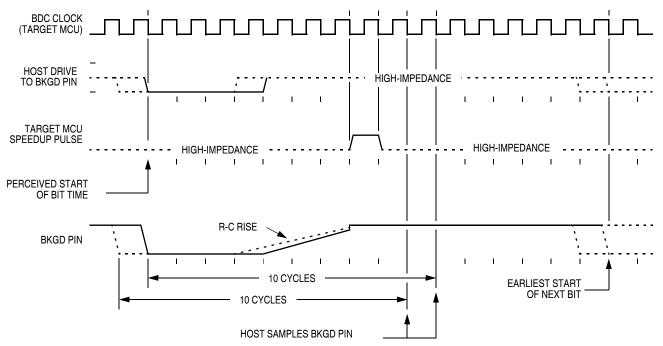

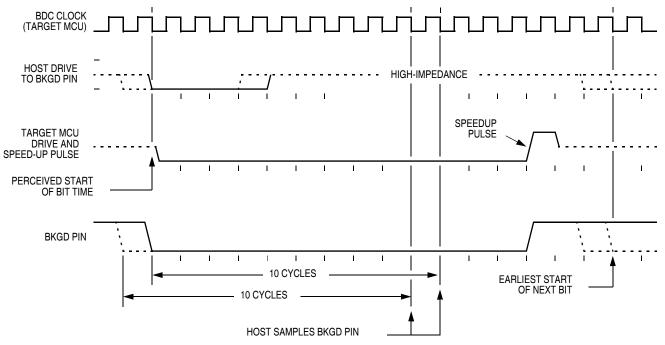

The BKGD/MS pin is used primarily with BDC communications, and features a custom protocol that uses 16 clock cycles of the target MCU's BDC clock per bit time. The target MCU's BDC clock can run as fast

as the bus clock, so no significant capacitance must be connected to the BKGD/MS pin that could interfere with background serial communications.

Although the BKGD/MS pin is a pseudo open-drain pin, the background debug communication protocol provides brief, actively driven, high speedup pulses to ensure fast rise times. Small capacitances from cables and the absolute value of the internal pullup device play a minimal role in determining rise and fall times on the BKGD/MS pin.

#### NOTE

Ensure this pin is not low when the part is coming out of POR or BDFR reset. Exit from stop2 causes POR, therefore POR includes the exit from stop2. Because the pin defaults to BKGD/MS function out of reset, a low value on this pin while coming out of POR or BDFR causes the part to boot into BDM mode. If this pin is not being used at all, it must be tied high. A pullup is recommended when using this pin as GPIO.

# 2.3.5 IRQ

The PTF2/IRQ pin can be used as a wakeup source for the MCU. For stop2 wakeup, this pin has an analog path which is enabled based on the input buffer enable for this pin, irrespective of whether or not this pin is configured as IRQ.

#### NOTE

Care needs to be taken that if this pin is configured as input, it is not low during stop2 mode, otherwise the part exits stop2 mode irrespective of whether this pin is configured as IRQ or not. This pin can be disabled as a wakeup source if it is configured as an output.

# 2.3.6 LCD Pins

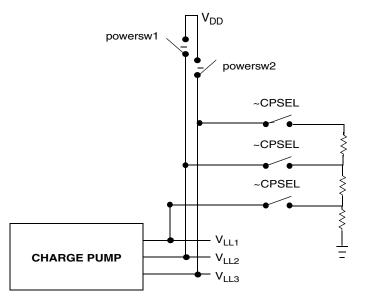

### 2.3.6.1 LCD Power Pins

The V<sub>LL1</sub>, V<sub>LL2</sub>, V<sub>LL3</sub>, V<sub>cap1</sub>, and V<sub>cap2</sub> pins are dedicated to providing power to the LCD module. On 64-pin and 80-pin packages the V<sub>LL3 2</sub> pin must be tied to V<sub>LL3</sub> on board. For more information about LCD pins, see Chapter 9, "LCD Module (S08LCDLPV1)."

### 2.3.6.2 LCD Driver Pins

The MC9S08LG32 series of MCUs provide 45 LCD driver pins for the 80-pin packages, 37 pins for the 64-pin packages, and 29 pins for the 48-pin packages. Each LCD pin has pin enable control, so you can choose to use any LCD pin as either LCD driver or GPIO. If the LCD module is disabled, the LCD driver pins become high-impedance and the LCD/GPIO pins are configured as GPIO. The LCD pins are open-drain after resets except for stop2 wakeup. For more information about LCD driver pins, see Chapter 9, "LCD Module (S08LCDLPV1)."

Pins that have shared function with the LCD have special behavior based on the state of the VSUPPLY bits in the LCDSUPPLY register. These pins can operate as full complementary drive or open drain drive

depending on the VSUPPLY bits. When  $V_{LL3}$  is connected to  $V_{DD}$  externally, VSUPPLY = 11, FCDEN = 1, and RVEN = 0, the pins operate as full complementary drive. For all other VSUPPLY modes, the LCD/GPIO operates as open drain.

#### NOTE

For GPIO muxed with LCD pins, full complimentary or open drain drive is controlled by the LCD controller. When LCD pins are configured as open drain GPIOs, then the internal pullup is not disabled in output mode and is controlled by the GPIO pull control register. This can cause some leakage from the pads if a pullup is enabled and a zero is being driven.

### 2.3.7 General-Purpose I/O (GPIO) and Peripheral Ports

The MC9S08LG32 series of MCUs support up to 69 GPIO pins including 2 output-only pins that are shared with on-chip peripheral functions (timers, serial I/O, LCD, ADC, etc.). The GPIO output-only pins (PTC5/BKGD/MS and PTC6/RESET) are bi-directional when configured as BKGD and RESET, respectively.

GPIO that is muxed with LCD pins can be configured to reference  $V_{DD}$  or  $V_{LL3}$ . See Section 2.3.6.2, "LCD Driver Pins," for more details.

When a port pin is configured as a general-purpose output or a peripheral uses the port pin as an output, the software can select one of the two drive strengths and can enable or disable the slew rate control. When a port pin is configured as a general-purpose input or a peripheral uses the port pin as an input, the software can enable a pullup device.

When an on-chip peripheral system is controlling a pin, the data direction control bits still determine what is read from port data registers even though the peripheral module controls the pin direction by controlling an enable for the pin's output buffer. For information about controlling these pins as general-purpose I/O pins, see Chapter 6, "Parallel Input/Output Control."

#### NOTE

- To avoid extra current drain from floating input pins, the reset initialization routine in the application program must either enable on-chip pullup devices or change the direction of unused or non-bonded pins to outputs so they do not float.

- When using RESET pin as bi-directional reset and LCD pins as open-drain GPIO, the internal pullups are not disabled when these pins are used in output mode. This can cause some current leakage through the pads if zero is driven. This is also true for stop2 mode.

| Packages |    | Packages < Lowest Priority> Highest |          |       |       |       |       |

|----------|----|-------------------------------------|----------|-------|-------|-------|-------|

| 80       | 64 | 48                                  | Port Pin | Alt 1 | Alt 2 | Alt 3 | Alt 4 |

| 1        | 1  | 1                                   | PTD7     | LCD7  |       | —     | _     |

| 2        | 2  | 2                                   | PTD6     | LCD6  | —     | —     | —     |

#### Table 2-1. Pin Availability by Package Pin-Count

| Packages |    |    | < Lowest <b>Priority</b> > Highest |                   |         |         |       |  |  |

|----------|----|----|------------------------------------|-------------------|---------|---------|-------|--|--|

| 80       | 64 | 48 | Port Pin                           | Alt 1             | Alt 2   | Alt 3   | Alt 4 |  |  |

| 3        | 3  | 3  | PTD5                               | LCD5              | —       | —       | _     |  |  |

| 4        | 4  | 4  | PTD4                               | LCD4              | —       | —       | _     |  |  |

| 5        | 5  | 5  | PTD3                               | LCD3              | —       | —       | _     |  |  |

| 6        | 6  | 6  | PTD2                               | LCD2              | _       | —       | _     |  |  |

| 7        | 7  | —  | PTB3                               | LCD32             | _       | —       | _     |  |  |

| 8        | 8  | —  | PTB2                               | LCD31             | —       | —       | _     |  |  |

| 9        | —  | —  | PTB7                               | LCD40             | —       | —       | _     |  |  |

| 10       | —  | —  | PTB6                               | LCD39             | —       | —       | _     |  |  |

| 11       | —  | —  | PTB5                               | LCD38             | —       | —       | _     |  |  |

| 12       | —  | —  | PTB4                               | LCD37             | —       | —       | _     |  |  |

| 13       | 9  | —  | PTB1                               | LCD30             | —       | —       | _     |  |  |

| 14       | 10 | —  | PTB0                               | LCD29             | —       | —       | _     |  |  |

| 15       | 11 | 7  | PTD1                               | LCD1              | —       | _       | _     |  |  |

| 16       | 12 | 8  | PTD0                               | LCD0              | —       | —       | —     |  |  |

| 17       | 13 | 9  | V <sub>CAP1</sub>                  |                   | —       | —       | —     |  |  |